### Keysight M8085A MIPI<sup>®</sup> D-PHY Editor

User Guide

### **Notices**

### © Keysight Technologies 2018-2019

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies as governed by United States and international copyright laws.

### **Trademarks**

MIPI $^{\otimes}$  C-PHY<sup>TM</sup> and MIPI $^{\otimes}$  D-PHY<sup>TM</sup> are registered trademarks of the MIPI Alliance.

### Manual Part Number

M8085-91040

### Edition

Edition 6.2, June 2019

Keysight Technologies Deutschland GmbH Herrenberger Strasse 130, 71034 Böblingen, Germany

### **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

### U.S. Government Rights

The Software is "commercial computer software," as defined by Federal Acquisition Regulation ("FAR") 2.101. Pursuant to FAR 12.212 and 27.405-3 and Department of Defense FAR Supplement

("DFARS") 227.7202, the U.S. government acquires commercial computer software under the same terms by which the software is customarily provided to the public. Accordingly, Keysight provides the Software to U.S. government customers under its standard commercial license, which is embodied in its End User License Agree-

ment (EULA), a copy of which can be found at http://www.kevsight.com/find/sweula.

The license set forth in the EULA represents the exclusive authority by which the U.S. government may use, modify, distribute, or disclose the Software. The EULA and the license set forth therein, does not require or permit, among other things, that Keysight: (1) Furnish technical information related to commercial computer software or commercial computer software documentation that is not customarily provided to the public; or (2) Relinguish to, or otherwise provide, the government rights in excess of these rights customarily provided to the public to use, modify, reproduce, release, perform, display, or disclose commercial computer software or commercial computer software documentation. No additional government requirements beyond those set forth in the EULA shall apply, except to the extent that those terms, rights, or licenses are explicitly required from all providers of commercial computer software pursuant to the FAR and the DFARS and are set forth specifically in writing elsewhere in the EULA. Keysight shall be under no obligation to update, revise or otherwise modify the Software. With respect to any technical data as defined by FAR 2.101, pursuant to FAR 12.211 and 27.404.2 and DFARS 227.7102. the U.S. government acquires no greater than Limited Rights as defined in FAR 27.401 or DFAR 227.7103-5 (c), as applicable in any technical data.

### Warranty

THE MATERIAL CONTAINED IN THIS DOCUMENT IS PROVIDED "AS IS," AND IS SUBJECT TO BEING CHANGED, WITHOUT NOTICE, IN FUTURE EDITIONS. FURTHER, TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, KEYSIGHT DISCLAIMS ALL WARRANTIES, EITHER EXPRESS OR IMPLIED WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED

HEREIN. INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MER-CHANTABILITY AND FITNESS FOR A PAR-TICULAR PURPOSE, KEYSIGHT SHALL NOT BE LIABLE FOR ERRORS OR FOR INCIDEN-TAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE. OR PERFORMANCE OF THIS DOCU-MENT OR ANY INFORMATION CONTAINED HEREIN. SHOULD KEYSIGHT AND THE USER HAVE A SEPARATE WRITTEN AGREE-MENT WITH WARRANTY TERMS COVER-ING THE MATERIAL IN THIS DOCUMENT THAT CONFLICT WITH THESE TERMS. THE WARRANTY TERMS IN THE SEPARATE AGREEMENT WILL CONTROL.

### Safety Notices

### **CAUTION**

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

### WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

### Contents

### 1 Introduction

# Overview 8 Modes supported by the MIPI D-PHY Editor 9 Data File Format (\*.dat or \*.txt) 10 Sequence File Format(\*.seq) 11 Automatic Clock Generation 15

**Sequence File Definition for CSI**

21

Understanding a DSI sequence file

Calculating HS Data Rate for the DSI sequence

Overview

### 2 Sequence File Definition for CSI and DSI

### Long and Short Packet Formats 21 23 Frame and Line Synchronization Packets Understanding a CSI sequence file Calculating HS Data Rate for CSI sequence 28 **Sequence File Definition for DSI** 30 30 Overview Long and Short Packet Formats 31 32 DSI Sequence Format Description 34 Transmission Packet Sequences 38 Replacing B-Macros with C-Macros in a sequence file

21

45

### 3 Using MIPI D-PHY Editor User Interface

### **Basic Requirements** 48

Hardware Setup using M8195A AWG Module 48

Software Requirements 50

License Requirements 50

Installing Plug-in 52

**Related Documents** 53

Starting the MIPI D-PHY Editor Plug-in 54

Contacting Keysight Technologies 56

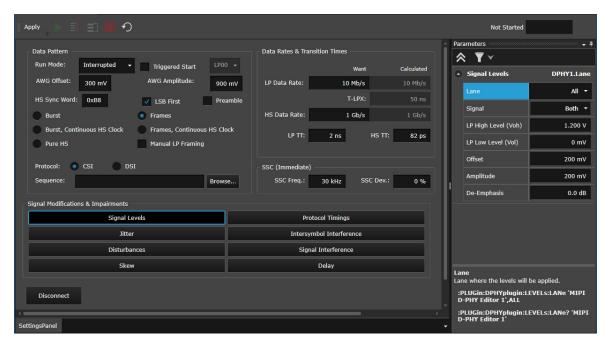

MIPI D-PHY Editor User Interface 57

Connection Setup 57

Main User Interface 65

### **Setting up MIPI D-PHY Editor Parameters** 76

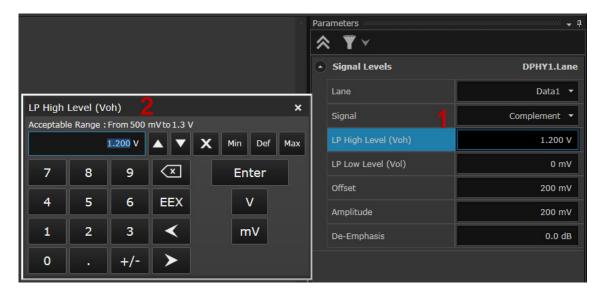

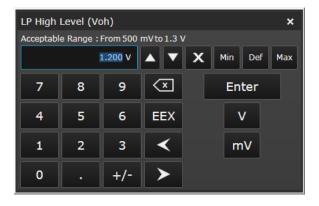

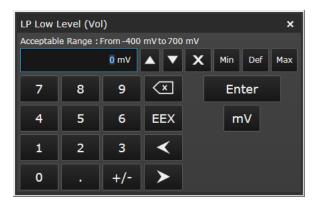

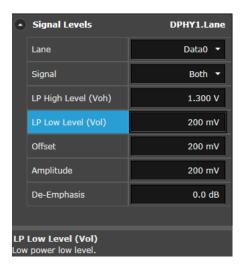

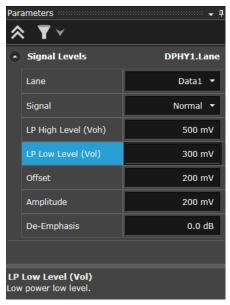

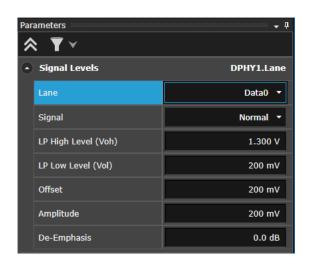

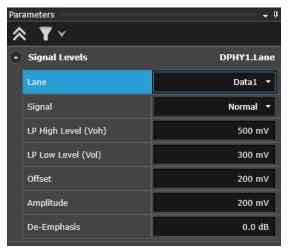

Signal Levels Group 77

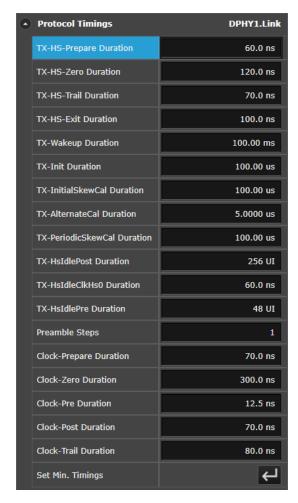

Protocol Timings 86

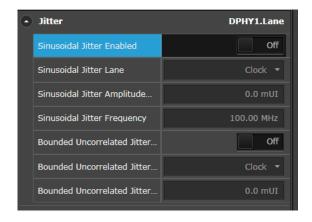

Jitter Group 88

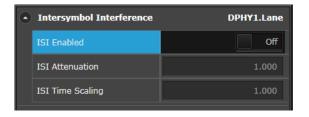

Intersymbol Interference Group 89

Disturbances Group 90

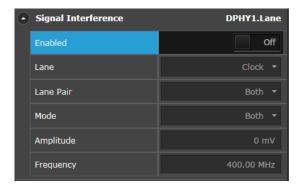

Signal Interference Group 95

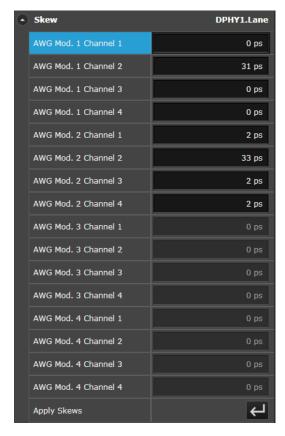

Skew Group 97

98

Delay Group

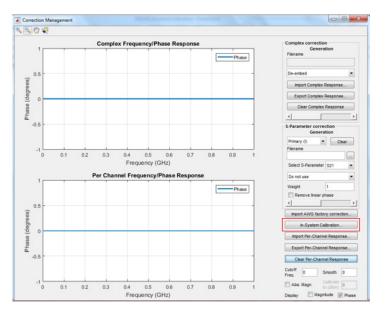

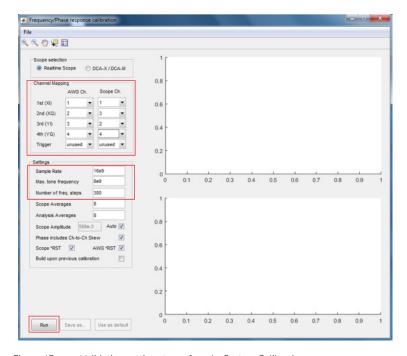

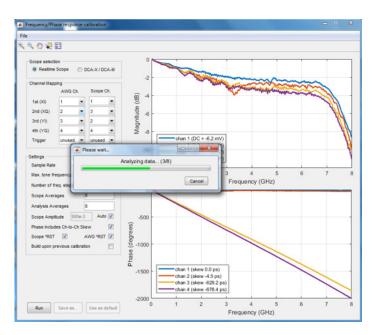

Performing In-System AWG Calibration with Keysight IQ Tools 99

### New Sequences in MIPI D-PHY 2.1 114

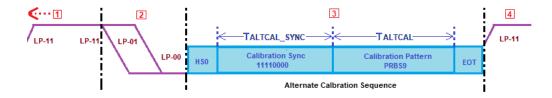

Understanding Alternate Calibration Sequence 114

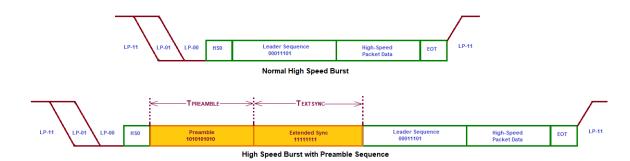

Understanding Preamble Sequence 116

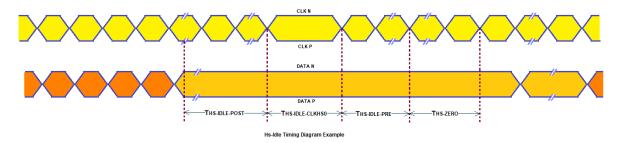

Understanding HS-Idle Sequence 117

### 4 SCPI Programming

### **SCPI Command Language** 122

Data Types 122

Important Points about SCPI 123

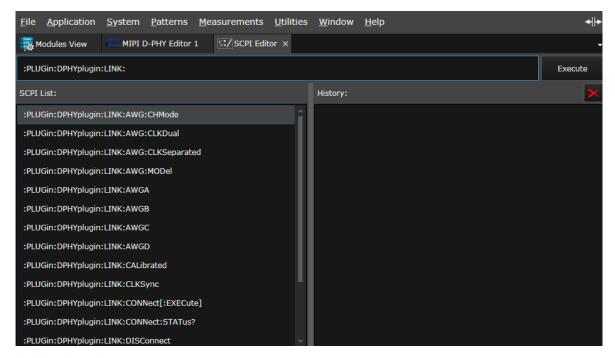

SCPI Editor 126

### SCPI Command Reference 128

SCPI Commands for Connection Group 128

SCPI Commands for Data Pattern Group 136

SCPI Commands for Data Rate and Transition Time Group 143

SCPI Command for Signal Levels Group 145

SCPI Commands for Protocol Timings Group 149

SCPI Commands for Jitter Group 158

SCPI Commands for Intersymbol Interference Group 162

SCPI Commands for Disturbances Group 164

SCPI Commands for Signal Interference Group 170

SCPI Commands for Skew Group 173

SCPI Commands for Delay Group 175

SCPI Commands for SSC Group 177

Other SCPI Commands 178

Remote Queries to find Parameter ranges (maximum and minimum

limits) 182

Contents

### 1 Introduction

Overview / 8

Data File Format (\*.dat or \*.txt) / 10

Sequence File Format(\*.seq) / 11

This chapter gives an overview on the high-speed serial interface called MIPI D-PHY, which provides high throughput performance over bandwidth limited channels for connecting to peripherals, along with an overview of the Keysight M8085A MIPI D-PHY Editor plug-in, the Data File and Sequence File definitions used in the MIPI D-PHY Editor plug-in.

### Overview

The M8070B software has an add-on **MIPI D-PHY Editor** that generates MIPI D-PHY signals so as to test the DUTs that are compatible to this standard.

MIPI D-PHY describes a source synchronous, high speed, low power, low cost PHY, especially suited for mobile applications. The MIPI D-PHY specification (http://mipi.org/) has been written primarily for the connection of camera and display applications to a host processor. Nevertheless, it can be applied to many other applications.

The MIPI D-PHY provides a synchronous connection between Master and Slave. A practical PHY Configuration consists of a clock signal and one or more data signals. The clock signal is unidirectional, originating at the Master and terminating at the Slave. The data signals can either be unidirectional or bi-directional depending on the selected options.

The PHY uses two wires per Data Lane plus two wires for the Clock Lane. This gives four wires for the minimum PHY configuration. In High-Speed mode, each Lane is terminated on both sides and driven by a low-swing, differential signal. In Low-Power mode all wires are operated single-ended and non-terminated.

The **MIPI D-PHY Editor** is a licensed feature. To enable the **MIPI D-PHY Editor**, the following licenses/options are required:

- System software license ("M8070B-0TP" or "M8070B-0NP")

- MIPI D-PHY Editor license ("refer to Chapter 3, License Requirements on page 50)

- M8195A AWG, which uses the following options:

- Option -001, -002, or -004: With these options the number of channels is selected. The M8195A is available in a one channel (-001), two channel (-002) or 4 channel (-004) version. A software upgrade from one to two channels is possible by installing option U02. A software upgrade from two to four channels is possible by installing option U04. In order to upgrade from one to four channels, first option -U02 and next -U04 must be installed.

- Option -16G: This option offers 16384 MSa (=16 GSa) waveform memory for the M8195A. Option -16G is software upgradeable.

- Option -SEQ: This option offers extensive sequencing capabilities.

Option -SEQ is software upgradeable.

- Option -FSW: This option enables the M8195A to externally select or step through segments or sequences faster than every 500 µs. Option -FSW is export controlled and is software upgradeable.

- Option -1A7, -Z54: Calibration options.

For more details on how to install these licenses, refer to *Keysight M8000* Series of BER Test Solutions User Guide.

### NOTE

You require the AWG large memory option (0G2) to test large patterns using the MIPI D-PHY Editor plug-in.

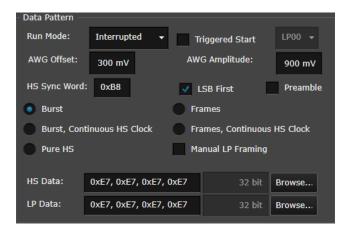

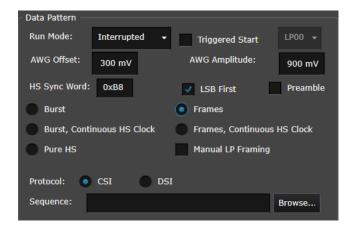

Modes supported by the MIPI D-PHY Editor

The MIPI D-PHY Editor plug-in supports two different mode groups:

- The Burst mode: In the Burst Modes (Burst, Burst Continuous Clock, Pure HS) a block of data is repeated infinitely. This block can contain LP Data and HS Data, pure LP data or pure HS data depending on the content of the data given for HS and LP. If either HS or LP data is empty (an empty text box for that particular data type), the software generates pure LP/HS data. If Pure HS is selected, no LP11 transitions are included and all LP data is neglected. The burst mode requires two sequences of data, one sequence for HS and other for LP. Each sequence can be set manually or be read by the software from a data file.A block consists of a name followed by one or more LP blocks:

- LP Blocks: The format is LPxyNn. x and y can be 0 or 1, depending on the desired LP state. n represents the number of LP states.

- The Frame mode: In these modes (Frames and Frames, Continuous HS Clock), a sequence file allows running a sequence of blocks ending with an infinite loop over the complete number of blocks or an selection of the last blocks. Each individual block can be repeated ("looped") N-times and the number of repetitions N can be selected for each block separately. In addition to the data files, the frame modes require a sequence file. It specifies the data rates and the sequence of blocks. The M8085A MIPI D-PHY Editor plug-in supports sequence files conforming to the CSI and DSI protocol standards. While the section below describes sequence file formats in general, refer to Sequence File Definition for CSI and DSI on page 17 to understand sequence file formats for CSI and DSI protocols respectively.

### Data File Format (\*.dat or \*.txt)

For data definition in the MIPI D-PHY Editor plug-in, the hexadecimal (HEX) format is required. Bytes are represented in two digits, each ranging from 0 to 9 and A to F. The leading string "0x" is optional. Supported separators between data bytes are:

- , (comma)

- ; (semicolon)

space (blank)

tab

line feed

nothing

Some examples:

- · 0x01, 0xF3, 0x23

- · 0134E734FF

- 32 FF E5 44

In addition to the pure HEX data, special commands are abbreviations of lists of hex bytes:

• 0x<HEX code>N<count>: repeat the byte <HEX code> <count> times.

For example: 0xABN5 is equal to AB AB AB AB AB.

• Ox<HEX code>S<count> repeat the byte <HexCode> N times for each data lane. In a one-data lane configuration the macro is similar to 0x<HEX code>N<count>, but in a multi-lane setup, it will repeat <HexCode> at each data lane <count> times.

For example, 0xABS4 is equal to AB AB AB in a 1-lane configuration, but will become AB AB AB AB at each data lane for a multi-lane setup.

An example for 2 data lanes:

0x02c05 is equal to D0: 02 03 04 05 and D1: 02 03 04 05.

For the counter with the "x" and two data lanes, 0x02x05 would lead to D0: 02 04 and D1: 03 05.

NOTE

The special commands require the leading "0x", otherwise they will not be recognized.

### Sequence File Format(\*.seq)

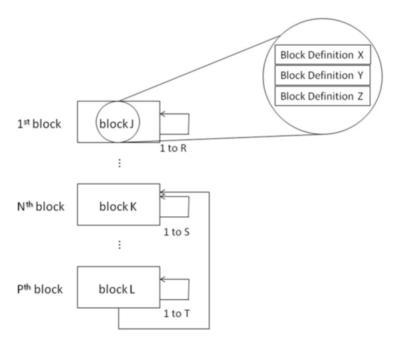

For waveform generation in the MIPI D-PHY Editor plug-in, you may use sequence files. In the sequence file the data rate, data blocks and sequence are defined. Note that all parameters are even integers. The structure of a sequence file is shown in Figure 1.

```

HSFreq: <frequency in bits/s>

Blocks:

<BlockName 1>: <Block Definition 1>, ..., <Block Definition n1>;

...

<BlockName M>: <Block Definition 1>, ..., <Block Definition nM>;

Sequence:

1. <BlockName J>, <Loop Count R>; - First block

...

<N>. <BlockName K>, <Loop Count S>; - Nth block

...

<P>. <BlockName L>, <Loop Count T>; - Pth block

[LoopTo N]

```

Figure 1 Block Diagram of a Sequence Example

Each block can comprise multiple sub-blocks (1 to n). Sub-blocks can be used in multiple blocks. In the sequence, blocks can be used as often as needed. Within the sequence, the LoopTo expression starts an infinite loop from block <N> to the last block <P>. If no LoopTo expression is specified, an infinite loop is created from block 1 to block P. Valid block definitions are:

- · LP00, LP01, LP10, LP11: for a single LP state.

- LP<LP state 00,01,10, or 11>[<LP state 00,01,10, or 11>...] Only available in the Manual LP Framing mode and for LP pattern. It allows a sequence of LP states to be defined in one statement.

For example: LP1101001011

LPB"<filename>": for generating LP data specified in the file with the name <filename>. The file should be in the same folder as the sequence file. At the beginning of the data an escape trigger for LP or ULP data mode is sent before the data and a Mark-0/1 sequence is sent after the end of the data. For the data, the data file format given above must be used.

- LP<00, 01, 10, or 11>N<number of bits>: The LP state is sent <number of [HS] bits> times.

- LP<00, 01, 10, or 11>E<number of bits>: The LP state is sent until the block size reaches the number of HS bits given in <number of bits>.

- LPHSE<number of bits>: The block is filled with LP11 states and a LP– HS transition until the number of HS bits <number of bits> is reached.

- LPHS: The macro adds a LP-HS transition. It is mainly for influencing the block ending. If for example the following block starts with HS data, then the LP-HS transition will done at the end of the actual block. Without this macro the LP-HS transition would be added to the beginning of the following block. You do not need the macro for the following B macros, since they will trigger a LP-HS transition automatically if the previous block description contained LP states.

- B"<filename>": for generating HS data given in the file <filename>. The file should be in the same folder as the sequence file. If necessary, a LP-to-HS transition is generated before the data. A HS-to-LP transition is added if the following block contains LP states.

- BL<number of blanking bytes>: for generating HS blanking packets with a number of blanking bytes given in <number of blanking bytes>.

The id (0x19), word counter, ECC (Error-Correcting Code) and CRC (Cyclic Redundancy Check) are calculated and added such that the number of bits is equal to (<number of blanking bytes>+6)\*8;

- C<3 hex bytes>: For generating short packets like they are described in the CSI or DSI specifications. The resulting short packet will have the first byte as Data ID of this packet and the following two bytes as Packet DATA followed by the ECC for that packet. If necessary, a LP-to-HS transition is generated before the data. A HS-to-LP transition is added if the following block contains LP states.

- C<1 hex byte>"<filename>": for generating a long packet. The content in the filename will be taken as payload. The header will have the given hex byte as ID followed by a two byte word counter, followed by a ECC for that header data. At the end of the payload, a two byte CRC is added. If necessary, an LP-to-HS transition is generated before the data. An HS-to-LP transition is added if the following block contains LP states.

- PRBS<no.>(<seed1>|<seed2>| ... | <seedN>): for generating a PRBS of the polynomial <no.> with a seed of <seed1-N> for each lane. The <no.> is just a decimal number (only 9 is allowed), and the seeds are given in a hex number (example 0x789A). The number of input seeds should be the same as active lanes (example for 3 lanes <seed1> goes to D0, <seed2> goes to D1 and <seed3> goes to D2). If #seeds > #lanes the latest seeds will be ignored. If #seeds < #lanes an exception will be thrown. As a special case, if only one seed is provided but more than one lane is active, the pattern is distributed among all lanes.

- ULPEntry: Adds the ULP Entry escape sequence to the block. After the ULPEntry LP00 states plus finally an ULPExit should follow to create a specification conform ULP sequence.

- ULPExit<number of LP10 states>: Creates a ULP exit sequence. It is not allowed to combine this block definitions with other definitions, which means in this case the block must only contain this macro and no other.

- InitialSkewCal: adds an HS clock pattern to all data lanes to generate the skew calibration block at the beginning of the data transmission (see MIPI Alliance Specification for D-PHY<sup>SM</sup> version 2.1). It is not allowed to combine this block definition with other definitions, which means in this case the block must only contain this macro and no other. The block before needs to contain a LPHSE or LPHS block as last entry to force the frame generator to put the special LP-HS transition for the sync pattern at the end of the previous block. In this case, the sync word is replaced by 0xFF. In the sequence definition the loop counter value for the block will be replaced by a suitable value to generate the clock pattern for duration TX-InitialSkewCal Duration parameter given via the Editor's user interface.

- PeriodicSkewCal: similar to InitialSkewCal, adds an HS clock pattern for line de-skew. This block is meant to be within the looped part of the pattern, and the same restriction as for InitialSkewCal apply. The duration of the line de-skew will be set by the **TX-PeriodicSkewCal Duration** parameter in the Editor's user interface.

### NOTE

- If blocks are looped, the beginning of the block should have the same kind of data mode (LP or HS) as the block following it, otherwise the block loop will result in invalid LP to HS transitions.

- Video Frames which contain LP11 blanking periods should be rotated so that the block definition always ends with a LP11E command.

- If only the header contains LP11 states, the header block should end with LPHSE to start the HS transmission at the end of the header block.

- In case of PureHS mode, an initial LP to HS transition is added in the form of a hidden intro block in the waveform generation, before an infinite loop of pure HS data stream is generated.

In any case to each sequence, an LP11 block is added to the beginning of the sequence. If required, an LP-HS transition is added if the first block starts with HS data. Also, a sync block is added for the synchronization of the ParBERT LP and HS subsystems. These blocks need not to be added explicitly to the sequence. They are added automatically for all sequences, that is, even if a sequence with pure HS blocks is given.

### Automatic Clock Generation

Depending on the data lane pattern, a clock lane signal is generated which adheres to the MIPI D-PHY standard. For every high speed burst on the data lane a transition from LP to HS will be done on the clock lane. The HS clock will be active as long as the HS burst on the data lane is active. After the HS data burst ended the clock lane will also transition back to its stop state in case the next HS burst on the clock is far enough away to fit in the transition segments. In case this LP mode is active for a shorter duration on the data lane the HS clock will stay active for both bursts and not transition back to clock LP mode.

1 Introduction

Keysight M8085A MIPI D-PHY Editor User Guide

## 2 Sequence File Definition for CSI and DSI

Sequence File Definition for CSI / 21 Sequence File Definition for DSI / 30

The following sections describe the various elements of a sequence file for the CSI and DSI protocols, such that the sequence file definition generates a waveform that conforms to the MIPI Specification for Camera Serial Interface (CSI) and MIPI Alliance Specification for Display Serial Interface (DSI), respectively.

Generally, a sequence file consists of three elements that form together a sequence:

- · HS Data Rate

- Blocks

- Sequence

Following is a real time example of a sequence file definition:

### **Example of a Sequence File Definition:**

HSFreq: 200MBit/s;

Blocks:

LPInit1: LPB"Esc0ms.txt",LP11E13728;

LPPause: LP11N1024;

LPInit2: LPB"Esc100ms.txt",LP11E13728;

LPInit3: LPB"Esc200ms.txt",LP11E13728;

Header: B"FirstHsLine.txt",LP11E6016;

Video: B"VideoLine.txt",LP11E6016;

### Sequence:

- 1 LPInit1,1;

- 2 LPPause,20000;

- 3 LPInit2,1;

- 4 LPPause,20000;

- 5 LPInit3,1;

- 6 LPPause,20000;

- 7 Header,1;

- 8 Video,319;

LoopTo 6;

Following are real time examples of DSI and CSI sequence file definitions, respectively:

### **Example of a DSI Sequence File Definition:**

HSFreg: 432.432MBit/s;

Blocks:

LPInit: LPB"HSyncEnd.txt",LP11E13728;

HSync: B"HSyncEnd.txt",LP11E12736,B"HSyncStart.txt",LP11E13728;

VSyncStart: B"HSyncEnd.txt",LP11E12736,B"VSyncStart.txt",LP11E13728;

VSyncEnd: B"HSyncEnd.txt",LP11E12736,B"VSyncEnd.txt",LP11E13728;

Video: B"HSyncEnd.txt",LP11E960,B"Video480pHSyncStart.txt",LP11E13728;

### Sequence:

- 1 LPInit,1;

- 2 HSync,5;

- 3 VSyncEnd,1;

- 4 HSync,29;

- 5 Video,480;

- 6 HSync,9;

- 7 VSyncStart,1;

LoopTo 2;

### **Example of a CSI Sequence File Definition:**

HSFreq: 158 MBit/s;

Blocks:

FrameStart: B"FrameStart.txt",LP11E10880;

Blanking: LP11E10880;

Video: C1E"compliance640\_480.txt",LP11E10880;

FrameEnd: B"FrameEnd.txt",LP11E2048;

### Sequence:

- 1 FrameStart,1;

- 2 Blanking,1;

- 3 Video,480;

- 4 Blanking,2;

- 5 FrameEnd,1;

### Sequence File Definition for CSI

### Overview

CSI is a MIPI Alliance standard for serial interface between a camera module and host processor. CSI adheres to the Low-Level Protocol (LLP), which is a byte orientated, packet based protocol that supports the transport of arbitrary data using Short and Long packet formats. Two packet structures are defined for low-level protocol communication: Long packets and Short packets. The format and length of Short and Long Packets depends on the choice of physical layer (MIPI C-PHY or MIPI D-PHY). For each packet structure, exit from the low power state followed by the Start of Transmission (SoT) sequence indicates the start of the packet. The End of Transmission (EoT) sequence followed by the low power state indicates the end of the packet. However, in CSI implementation, one burst consists of only one packet and LP11 state must be inserted before the start of a burst. Since it requires to go to LP state always, an explicit EoT packet is not required.

### NOTE

A sequence file used for MIPI D-PHY or MIPI C-PHY conformance testing cannot be used for CSI/DSI conformance testing unless the header, payload and checksum data is included in the CSI/DSI block definitions in the sequences else the device rejects the packet.

Long and Short Packet Formats

### Long Packet

For MIPI D-PHY, a Long Packet shall be identified by Data Types 0x10 to 0x37. A Long Packet for the MIPI D-PHY physical layer option shall consist of three elements: a 32-bit Packet Header (PH), an application specific Data Payload with a variable number of 8-bit data words, and a 16-bit Packet Footer (PF). The Packet Header is further composed of three elements: an 8-bit Data Identifier, a 16-bit Word Count field and an 8-bit ECC. The Packet footer has one element, a 16-bit checksum (CRC).

For C-PHY, the Long Packet structure for the C-PHY physical layer option shall consist of four elements: a Packet Header (PH), an application specific Data Payload with a variable number of 8-bit data words, a 16-bit Packet Footer (PF), and zero or more Filler bytes (FILLER). The Packet Header is 6N x 16-bits long, where N is the number of C-PHY physical layer Lanes. The Packet Header consists of two identical 6N-byte halves, where each half consists of N sequential copies of each of the following

fields: a 16-bit field containing eight Reserved bits plus the 8-bit Data Identifier (DI); the 16-bit Packet Data Word Count (WC); and a 16-bit Packet Header checksum (PH-CRC) which is computed over the previous four bytes. The value of each Reserved bit shall be zero. The Packet Footer consists of a 16-bit checksum (CRC) computed over the Packet Data using the same CRC polynomial as the Packet Header CRC and the Packet Footer used in the MIPI D-PHY physical layer option. Packet Filler bytes are inserted after the Packet Footer, if needed, to ensure that the Packet Footer ends on a 16-bit word boundary and that each MIPI D-PHY physical layer Lane transports the same number of 16-bit words (i.e. byte pairs).

For both physical layer options, the 8-bit Data Identifier field and the 16-bit Word Count (WC) field contain identical data. The CSI receiver reads the next WC 8-bit data words of the Data Payload following the Packet Header. The length of the Data Payload shall always be a multiple of 8-bit data words. For both physical layer options, once the CSI receiver has read the Data Payload, it then reads the 16-bit checksum (CRC) in the Packet Footer and compares it against its own calculated checksum to determine if any Data Payload errors have occurred.

In either case, Packet Data length = Word Count (WC) \* Data Word Width (8-bits).

### **Short Packet**

For each option (MIPI C-PHY and MIPI D-PHY), the Short Packet structure matches the Packet Header of the corresponding Low Level Protocol Long Packet structure with the exception that the Packet Header Word Count (WC) field shall be replaced by the Short Packet Data Field. A Short Packet shall be identified by Data Types 0x00 to 0x0F. A Short Packet shall contain only a Packet Header; neither Packet Footer nor Packet Filler bytes shall be present. For Frame Synchronization Data Types, the Short Packet Data Field shall be the frame number. For Line Synchronization Data Types, the Short Packet Data Field shall be the line number.

For the MIPI D-PHY physical layer option, the Error Correction Code (ECC) byte allows single-bit errors to be corrected and 2-bit errors to be detected in the Short Packet.

For the C-PHY physical layer option, the 16-bit Checksum (CRC) allows one or more bit errors to be detected in the Short Packet but does not support error correction.

Short Packet Data Types shall be transmitted using only the Short Packet format. Refer to *Table 6 Synchronization Short Packet Data Type Codes* of the *MIPI Alliance Specification for Camera Serial Interface (CSI)*, which indicates that Data Type for Frame Start Code is 0x00 and Data Type for Frame End Code is 0x01.

NOTE

Between Low Level Protocol packets, there must always be an HS-LP or an LP-HS transition.

Frame and Line Synchronization Packets

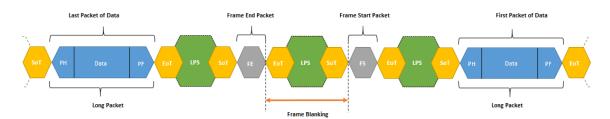

### Frame Synchronization Packets

Each image frame shall begin with a Frame Start (FS) Packet containing the Frame Start Code. The FS Packet shall be followed by one or more long packets containing image data and zero or more short packets containing synchronization codes. Each image frame shall end with a Frame End (FE) Packet containing the Frame End Code. For FS and FE synchronization packets, the Short Packet Data Field shall contain a 16-bit frame number. This frame number shall be the same for the FS and FE synchronization packets corresponding to a given frame.

### Line Synchronization Packets

Line synchronization packets are optional. For Line Start (LS) and Line End (LE) synchronization packets, the Short Packet Data Field shall contain a 16-bit line number. This line number shall be the same for the LS and LE packets corresponding to a given line.

### Frame Blanking and Line Blanking

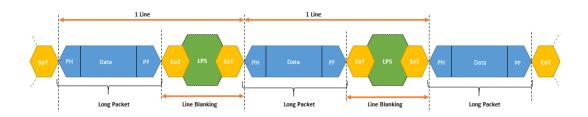

Figure 2 Block Diagram depicting packet structure for CSI sequence

**Frame Blanking** – The period between the Frame End packet in frame N and the Frame Start packet in frame N+1 is called the Frame Blanking Period

**Line Blanking** – The period between the end of the Packet Footer (or the Packet Filler, if present) of one long packet and the Packet Header of the next long packet is called the Line Blanking Period.

### Packet Data Payload Size Rules

For YUV, RGB or RAW data types, one long packet shall contain one line of image data. The total size of payload data within a long packet for all data types shall be a multiple of eight bits. The packet payload data format shall agree with the Data Type value in the Packet Header. Refer to Section 11 Data Formats, Table 3 - Data Type Classes for eight different data type classes and Table 8 - Primary and Secondary Data Formats Definitions of the MIPI Alliance Specification for Camera Serial Interface (CSI).

To understand the concept of sequences in CSI implementation, consider the block diagram of a video packet shown below.

KEY:

PH – Packet Header PF – Packet Footer + Filler (if applicable)

FS – Frame Start

FE – Frame End

LS – Line Start

LE – Line End

Figure 3 Block Diagram of a CSI Video Frame

For each video line transmission, the short packet or the FrameStart (FS) indicates start of transmission of the video packet. The payload data, which is contained in a long packet, consists of the Packet Header (PH),

followed by the actual arbitrary data and ending with the Packet Footer (PF). Another short packet or the FrameEnd (FE) indicates the end of transmission of the video packet. This data burst is in an HS state.

A Line Blanking (LP state) is transmitted between each video line, that is, after the end of a Packet Footer (PF) till the beginning of the next Packet Header (PH).

A Frame Blanking (LP state) is transmitted between each video frame, that is, after the end of a FrameEnd (FE) till the beginning of the next FrameStart (FS) short packet.

### Understanding a CSI sequence file

The description of the block diagram corroborates the structure of the CSI sequence file shown below, for CSI implementation. Note that all the text files defined in the sequence must be placed in the same folder directory where the sequence file is located.

HSFreq: 158 MBit/s;

### Blocks:

FrameStart: B"FrameStart.txt",LP11E10880;

Blanking: LP11E10880;

Video: C1E"compliance640\_480.txt",LP11E10880;

FrameEnd: B"FrameEnd.txt",LP11E2048;

### Sequence:

- 1. FrameStart,1;

- 2. Blanking,1;

- 3. Video,480;

- 4. Blanking, 2;

- 5. FrameEnd,1;

The sequence definition in the given example contains an intrinsic looping. In the sequence, the blanking lines generate the frame blanking, and the video lines contain the line blanking, which is generated by the LP states. The number of lines for the video data and the associated blanking is defined by the device manufacturer. The sequence begins with the

FrameStart block running once, followed by a Blanking line. Then, the Video block runs for 480 lines ending with another Blanking line, followed by the FrameEnd block running once. This sequence loops over until manually aborted.

If considered closely, the FrameStart block generates the Frame Start (FS) short packet, with the Frame Start Code 0x00 as its header. This follows an HS-LP transition using LP11, where a line blanking is performed with an LPE marker, which fills the LP states until 10880 HS states are attained. The Blanking block generates a frame blanking packet of LP11, which fills the LP states until 10880 HS states are attained and is generated to provide for the LP-HS transition before the actual video payload begins transmitting. In the Video block, the C-Macro with a 1-byte data type of 0x1E generates the Packet Header of the long packet, followed by the actual payload video data (in Hex format) in the compliance640\_480.txt file.

Since the video data is High-Speed, the end of the video packet follows an HS to LP transition with a line blanking packet of LP11, which fills the LP states until 10880 HS states are attained. Two blanking lines are sent to indicate the end of the video payload data and to save energy. The FrameEnd block generates the Frame End (FE) short packet, with the Frame End Code 0x01 as its header. This follows an HS-LP transition with a line blanking packet of LP11, which fills the LP states until 2046 HS states are attained.

Some other points to note are:

- Since you cannot send more than one packet per burst, Blanking (LP state) is inserted at the end of each burst to avoid HS data from concatenating.

- The length of the line and frame blanking is device dependent.

- The data type 0x1E corresponds to the pixel color code YUV422 8-bit used in the video. Refer to Section 11 Data Formats of the MIPI Alliance Specification for Camera Serial Interface (CSI) for more information about the other Data Types for various color codes.

- The line blanking length and bits per pixel of a specific color code helps you in determining the total line length in HS states. The E-marker is used for the LP states instead of N, such that it fills up the blocks until the total defined length of HS States is attained.

NOTE

To retain the same line rate for CSI implementation between MIPI D-PHY and MIPI C-PHY, it is recommended that you keep the number of HS states equal in the LP definition.

If all lines in a sequence file definition have an LPE statement in the end, you may calculate the Frame Rate:

- 1 Multiply the number of lines with the number defined in the LPE statement of the sequence file definition.

- 2 Repeat step 1 for all lanes in the frame and add the resulting values for each lane.

- 3 Multiply the sum of all lanes with the HS period length, which derives the Frame Rate

### Calculating HS Data Rate for CSI sequence

To calculate the minimum HS data rate required to run the sequence, you must be aware of at least the frame rate and the device's display resolution, which is provided by the device manufacturer. The HS Frequency is the first line in the definition of a sequence file.

For example, let us consider that the device under test has a Frame Rate of 30~Hz and a display resolution of 640~x~480 pixels, where 640~is the horizontal resolution (or the length of each line) and 480~is the vertical resolution (or the number of video lines).

1 Calculate the line rate using the equation:

Line Rate = Frame Rate \* Vertical Resolution

However, the number of video lines has certain number of blanking lines preceding and following the video data, which must be considered as well for data rate calculation. The equation for line rate is, therefore, modified to:

Line Rate = Frame Rate \* (Vertical Resolution + no. of blanking lines) Let us assume that there are 10 blanking lines in a frame.

In this case, Line Rate = 30 Hz \* (480 + 10) = 14700 Hz

- 2 Determine the total length of lines in HS states.

- i Determine the number of bits required for transmission of the video data. To do so, check the pixel color coding for the Data Type in the video. In this case, the pixel color code is YUV422, which uses 8-bit per pixel.

Total no. of bits per line = Bit-size per pixel \* Horizontal resolution

In this case, Total no. of bits = 8 \* 640 = 5120 bits per line.

ii The number of bits for video transmission is not sufficient for determining the total length of lines in HS states, since extra time is required for the LP states in the line blanking. Therefore,

you must consider the LP states and accordingly extend the bits per line. Considering these factors, a total length of 10880 lines in HS states can be safely used for calculation of the HS data rate.

3 Calculate the HS Data Rate using the equation: Data Rate = Line Rate \* Total length of lines in HS state In this case, Data Rate = 14700 Hz x 10880 = 159.936 Mbps

Therefore, you can define the HS Data Rate (HSFreq) in the beginning of the sequence file, as shown in the example above.

For information on the CSI implementation in the MIPI D-PHY and MIPI C-PHY physical layer and detailed understanding of the protocol layer, refer to the MIPI Alliance Specification for Camera Serial Interface (CSI).

### Sequence File Definition for DSI

### Overview

DSI specifies the interface between a host processor and a peripheral such as a display module. It builds on existing MIPI Alliance specifications by adopting pixel formats and command set specified in DPI-2, DBI-489 2 and DCS standards. Some significant differences between DSI and CSI are:

- CSI uses unidirectional high-speed Link, whereas DSI is half-duplex bidirectional Link

- CSI makes use of a secondary channel, based on I2C, for control and status functions

- CSI data direction is from peripheral (Camera Module) to host processor, while DSI's primary data direction is from host processor to peripheral (Display Module)

- CSI sequence file structure is different from that of the DSI sequence file structure. The former consists of only of the FrameStart and FrameEnd packet along with some blanking lines, whereas the latter consists of HSync, VSync and Blanking packages.

At the lowest level, DSI protocol specifies the sequence and value of bits and bytes traversing the interface. It specifies how bytes are organized into defined groups called packets. The protocol defines required headers for each packet, and how header information is generated and interpreted.

On the transmitter side of a DSI Link, parallel data, signal events, and commands are converted in the Protocol layer to packets, following the packet organization. The Protocol layer appends packet-protocol information and headers, and then sends complete bytes through the Lane Management layer to the PHY. Packets are serialized by the PHY and sent across the serial Link. The receiver side of a DSI Link performs the converse of the transmitter side, decomposing the packet into parallel data, signal events and commands.

If there are multiple Lanes, the Lane Management layer distributes bytes to separate PHYs, one PHY per Lane, as described in Section 6 of the MIPI Alliance Specification for Display Serial Interface (DSI). Packet protocol and formats are independent of the number of Lanes used. The DSI protocol permits multiple packets to be concatenated, which substantially boosts effective bandwidth. This is useful for events such as peripheral initialization, where many registers may be loaded with separate write commands at system startup. There are two modes of data transmission, HS and LP transmission modes, at the PHY layer. Before an HS transmission can be started, the transmitter PHY issues a SoT sequence to

the receiver. After that, data or command packets can be transmitted in HS mode. Multiple packets may exist within a single HS transmission and the end of transmission is always signaled at the PHY layer using a dedicated EoT sequence. To enhance the overall robustness of the system, DSI defines a dedicated EoT packet (EoTp) at the protocol layer for signaling the end of HS transmission. In HS mode, time gaps between packets shall result in separate HS transmissions for each packet, with a SoT, LPS, and EoT issued by the PHY layer between packets. This constraint does not apply to LP transmissions.

### Long and Short Packet Formats

Two packet structures are defined for low-level protocol communication: Long packets and Short packets. For both packet structures, the Data Identifier (DI) is always the first byte of the packet, which includes information specifying the type of the packet.

### Long Packet

A Long packet shall consist of three elements: a 32-bit Packet Header (PH), an application-specific Data Payload with a variable number of bytes, and a 16-bit Packet Footer (PF). The Packet Header is further composed of three elements: an 8-bit Data Identifier, a 16-bit Word Count, and 8-bit ECC. The Packet Footer has one element, a 16-bit checksum. Long packets can be from 6 to 65,541 bytes in length.

After the end of the Packet Header, the receiver reads the next Word Count multiplied by the bytes of the Data Payload.

Once the receiver has read the Data Payload it reads the Checksum in the Packet Footer. The host processor shall always calculate and transmit a Checksum in the Packet Footer. Peripherals are not required to calculate a Checksum. Also, note the special case of zero-byte Data Payload: if the payload has length 0, the Checksum calculation results in (0xFFFF). If the Checksum is not calculated, the Packet Footer shall consist of two bytes of all zeros (0x0000). In the generic case, the length of the Data Payload shall be a multiple of bytes. In addition, each data format may impose additional restrictions on the length of the payload data, e.g. multiple of four bytes.

### **Short Packet**

A Short packet shall contain an 8-bit Data ID followed by two command or data bytes and an 8-bit ECC; a Packet Footer shall not be present. Short packets shall be four bytes in length. The Error Correction Code (ECC) byte allows single-bit errors to be corrected and 2-bit errors to be detected in the Short packet. Some short packets may also contain some data in the payload.

Long and Short packets have several common elements. The first byte of any packet is the DI (Data Identifier) byte. The Error Correction Code allows single-bit errors to be corrected and 2-bit errors to be detected in the Packet Header. The host processor shall always calculate and transmit an ECC byte. Peripherals shall support ECC in both forward- and reverse-direction communications.

DSI Sequence Format Description

### Sync Event (H Start, H End, V Start, V End), Data Type = XX 0001 (0xX1)

Sync Events are Short packets and, therefore, can time-accurately represent events like the start and end of sync pulses. As "start" and "end" are separate and distinct events, the length of sync pulses, as well as position relative to active pixel data, e.g. front and back porch display timing, may be accurately conveyed to the peripheral. The Sync Events are defined as follows:

- Data Type = 00 0001 (0x01) V Sync Start

- Data Type = 01 0001 (0x11) V Sync End

- Data Type = 10 0001 (0x21) H Sync Start

- Data Type = 11 0001 (0x31) H Sync End

To represent timing information as accurately as possible a V Sync Start event represents the start of the VSA. It also implies an H Sync Start event for the first line of the VSA. Similarly, a V Sync End event implies an H Sync Start event for the last line of the VSA.

Sync events should occur in pairs, Sync Start and Sync End, if accurate pulse-length information must be conveyed. Alternatively, if only a single point (event) in time is required, a single sync event (normally, Sync Start) may be transmitted to the peripheral. Sync events may be concatenated with blanking packets to convey inter-line timing accurately and avoid the overhead of switching between LPS and HS for every event. Display modules that do not need traditional sync/blanking/pixel timing should transmit pixel data in a high-speed burst then put the bus in Low Power Mode, for reduced power consumption.

### EoTp, Data Type = $00\ 1000\ (0x08)$

This short packet is used for indicating the end of a HS transmission to the data link layer. Therefore, detection of the end of HS transmission may be decoupled from physical layer characteristics. The main objective of the EoTp is to enhance overall robustness of the system during HS transmission mode. Therefore, DSI transmitters should not generate an EoTp when transmitting in LP mode. The Data Link layer of DSI receivers

shall detect and interpret arriving EoTps regardless of transmission mode (HS or LP modes) to decouple itself from the physical layer. Unlike other DSI packets, an EoTp has a fixed format as follows:

- Data Type = DI [5:0] = 0b001000

- Virtual Channel = DI [7:6] = 0b00

- Payload Data [15:0] = 0x0F0F

- ECC [7:0] = 0x01

### Blanking Packet (Long), Data Type = 01 1001 (0x19)

A Blanking packet is used to convey blanking timing information in a Long packet. Normally, the packet represents a period between active scan lines of a Video Mode display, where traditional display timing is provided from the host processor to the display module. The blanking period may have Sync Event packets interspersed between blanking segments. Like all packets, the Blanking packet contents shall be an integer number of bytes. Blanking packets may contain arbitrary data as payload.

The Blanking packet consists of the DI byte, a two-byte WC, an ECC byte, a payload of length WC bytes, and a two-byte checksum.

### Packed Pixel Stream, 16-bit Format, Long Packet, Data Type 00 1110 (0x0E)

This long packet (shown in the sequence example) is used to transmit image data formatted as 16-bit pixels to a Video Mode display module. The packet consists of the DI byte, a two-byte WC, an ECC byte, a payload of length WC bytes and a two-byte checksum.

### Packet Header Error Detection/Correction

The host processor in a DSI-based system shall generate an error-correction code (ECC) and append it to the header of every packet sent to the peripheral. The ECC takes the form of a single byte following the header bytes. The ECC byte shall provide single-bit error correction and 2-bit error detection for the entire Packet Header.

### Checksum Generation for Long Packet Payloads

Long packets are comprised of a Packet Header protected by an ECC byte and a payload of 0 to 216-1 bytes. To detect errors in transmission of Long packets, a checksum is calculated over the payload portion of the data packet. Note that, for the special case of a zero-length payload, the 2-byte checksum is set to 0xFFFF.

Checksum generation and transmission is mandatory for host processors sending Long packets to peripherals. It is optional for peripherals transmitting Long packets to the host processor. However, the format of Long packets is fixed; peripherals that do not support checksum generation shall transmit two bytes having value 0x0000 in place of the checksum bytes when sending Long packets to the host processor. The host processor shall disable checksum checking for received Long packets from peripherals that do not support checksum generation.

NOTE

An ECC byte can be applied to both Short and Long packets. Checksum bytes shall only be applied to Long packets.

### Transmission Packet Sequences

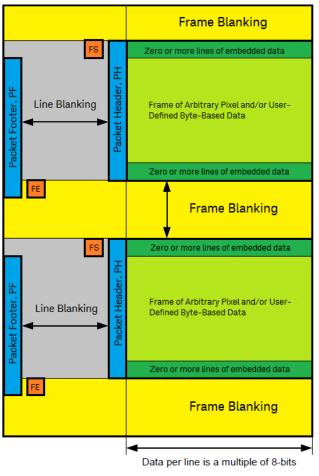

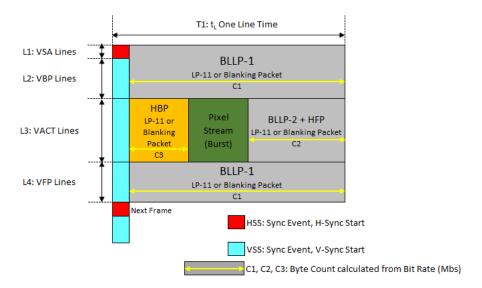

DSI supports several formats, or packet sequences, for Video Mode data transmission. The peripheral timing requirements dictate which format is appropriate. In the following sections, Burst Mode refers to time-compression of the RGB pixel (active video) portion of the transmission

### Non-Burst Mode with Sync Pulses

This mode enables the peripheral to accurately reconstruct original video timing, including sync pulse widths. Normally, periods shown as HSA (Horizontal Sync Active), HBP (Horizontal Back Porch) and HFP (Horizontal Front Porch) are filled by Blanking Packets, with lengths (including packet overhead) calculated to match the period specified by the peripheral data sheet. Alternatively, if there is sufficient time to transition from HS to LP mode and back again, a timed interval in LP mode may substitute for a Blanking Packet, thus saving power. During HSA, HBP and HFP periods, the bus should stay in the LP-11 state.

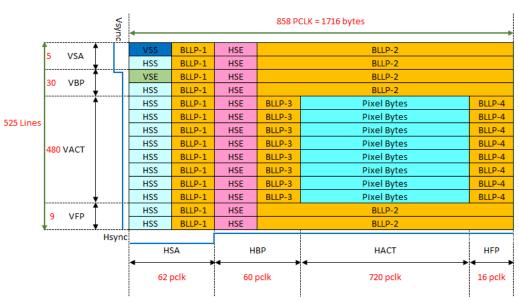

### Values in Red text are for a vertical resolution of 480p. Active image size is 720PCLK (Horizontal) x 480 Lines (Vertical).

Figure 4 Block Diagram for Video transmission in Non-Burst mode with Sync Pulses

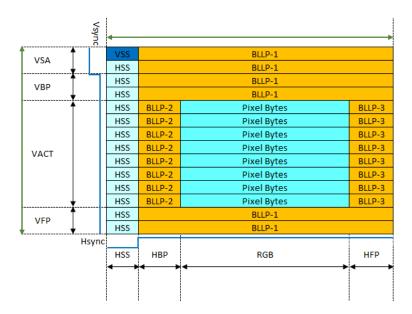

### Non-Burst Mode with Sync Events

This mode functions in the same manner as the previous mechanism, but accurate reconstruction of sync pulse widths is not required, so a single Sync Event is substituted. Here, only the start of each synchronization pulse (VSyncSHSyncStart and HSyncStart) is transmitted. The peripheral may regenerate sync pulses as needed from each Sync Event packet received. Pixels are transmitted at the same rate as they would in a corresponding parallel display interface such as DPI-2. As with the previous Non-Burst Mode, if there is sufficient time to transition from HS to LP mode and back again, a timed interval in LP mode may substitute for a Blanking Packet, thus saving power.

Figure 5 Block Diagram for Video transmission in Non-Burst mode with Sync Events

### **Burst Mode**

RGB pixel packets are time-compressed, leaving more time during a scan line for LP mode (saving power) or for multiplexing other transmissions onto the DSI link. In this mode, blocks of pixel data can be transferred in a shorter time using a time-compressed burst format. This is a good strategy to reduce overall DSI power consumption, as well as enabling larger blocks of time for other data transmissions over the Link in either direction. In the same manner as the Non-Burst Mode scenario, if there is sufficient time to transition from HS to LP mode and back again, a timed interval in LP mode may substitute for a Blanking Packet, thus saving power.

Figure 6 Block Diagram for Video transmission in Burst mode

Note that for accurate reconstruction of timing, packet overhead including Data ID, ECC, and Checksum bytes should be taken into consideration.

To enable PHY synchronization the host processor should periodically end HS transmission and drive the Data Lanes to the LP state. This transition should take place at least once per frame; The host processor should return to LP state once per scan-line during the horizontal blanking time. Regardless of the frequency of BLLP periods, the host processor is responsible for meeting all documented peripheral timing requirements. Note, at lower frequencies BLLP periods will approach, or become, zero, and burst mode will be indistinguishable from non-burst mode.

The sequence of packets within the BLLP or RGB portion of a HS transmission is arbitrary. The host processor may compose any sequence of packets, including iterations, within the limits of the packet format definitions. For all timing cases, the first line of a frame shall start with VSS; all other lines shall start with VSE or HSS. Note that the position of synchronization packets, such as VSS and HSS, in time is of utmost importance since this has a direct impact on the visual performance of the display panel.

# Replacing B-Macros with C-Macros in a sequence file

Table 1 shows how a sequence file written originally using the B-Macros can be alternatively written using C-Macros.

Table 1 Sequence file definition using B-Macros and C-Macros

| Sequence File Definition using B-Macro                                      | Sequence File Definition using C-Macro                                       |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------|

| HSFreq: 432.432MBit/s;                                                      | HSFreq: 432.432MBit/s;                                                       |

| Blocks:                                                                     | Blocks:                                                                      |

| LPInit: LPB"HSyncEnd.txt",LP11E13728;                                       | LPInit: LPB"HSyncEnd.txt",LP11E13728;                                        |

| HSync: B"HSyncEnd.txt",LP11E12736,B"HSyncStart.txt",LP11E13728; VSyncStart: | HSync: C310000,C080F0F,LP11E12736,C210000,C080F0F,LP11E13728;<br>VSyncStart: |

| B"HSyncEnd.txt",LP11E12736,B"VSyncStart.txt",LP11E13728;<br>VSyncEnd:       | C310000,C080F0F,LP11E12736,C010000,C080F0F,LP11E13728;<br>VSyncEnd:          |

| B"HSyncEnd.txt",LP11E12736,B"VSyncEnd.txt",LP11E13728;                      | C310000,C080F0F,LP11E12736,C110000,C080F0F,LP11E13728;                       |

| Video:                                                                      | Video:                                                                       |

| B"HSyncEnd.txt",LP11E960,B"Video480pHSyncStart.txt",LP11E13728;             | C310000,C080F0F,LP11E960,C0E"Video480p.txt",BL20,C210000,C080F0F             |

| Sequence:                                                                   | ,LP11E13728;                                                                 |

| 1. LPInit,1;                                                                | Sequence:                                                                    |

| 2. HSync,9;                                                                 | 1. LPInit,1;                                                                 |

| 3. VSyncStart,1;                                                            | 2. HSync,9;                                                                  |

| 4. HSync,5;                                                                 | 3. VSyncStart,1;                                                             |

| 5. VSyncEnd,1;                                                              | 4. HSync,5;                                                                  |

| 6. HSync,29;                                                                | 5. VSyncEnd,1;                                                               |

| 7. Video,480;                                                               | 6. HSync,29;                                                                 |

| LoopTo 2;                                                                   | 7. Video,480;                                                                |

|                                                                             | LoopTo 2;                                                                    |

Upon considering each block closely, we notice the following differences, otherwise the rest of the sequence definition remains the same.

- In the HSync block, the B"HSyncEnd.txt" is replaced by C310000,C080F0F and B"HSyncStart.txt" is replaced by C210000,C080F0F.

- In the VSyncStart block, the B"HSyncEnd.txt" is replaced by C310000,C080F0F and B"VSyncStart.txt" is replaced by C010000,C080F0F.

- In the VSyncEnd block, the B"HSyncEnd.txt" is replaced by C310000,C080F0F and B"VSyncEnd.txt" is replaced by C110000.C080F0F.

- In the Video block, the B"HSyncEnd.txt" is replaced by C310000,C080F0F and B"Video480pHSyncStart.txt" is replaced by C0E"Video480p.txt",BL20,C210000,C080F0F.

To understand how the replacements were done, you must read the description given in the earlier sections about the B"<filename>" macro, C<3 hex bytes> and C<1 hex byte>" <filename>" macros.

Let us consider the contents of each text file closely.

# Contents of HSyncEnd.txt

3100 0001

080F 0F01

As mentioned in the previous sections, the Data Type for the HSyncEnd signal is 0x31, which means this short packet has its Data ID as 31 and the following two bytes of Packet DATA as 00 00 followed by the ECC of 01.

Therefore, in a sequence, B"HSyncEnd.txt" can be written using the C<3 hex bytes> macro as C310000.

## Contents of HSyncStart.txt

2100 0012

080F 0F01

As mentioned in the previous sections, the Data Type for the HSyncStart signal is 0x21, which means this short packet has its Data ID as 21 and the following two bytes of Packet DATA as 00 00 followed by the ECC of 12.

Therefore, in a sequence, B"HSyncStart.txt" can be written using the C<3 hex bytes> macro as C210000.

#### Contents of VSyncEnd.txt

1100 0014

080F 0F01

As mentioned in the previous sections, the Data Type for the VSyncEnd signal is 0x11, which means this short packet has its Data ID as 11 and the following two bytes of Packet DATA as 00 00 followed by the ECC of 14.

Therefore, in a sequence, B"VSyncEnd.txt" can be written using the C<3 hex bytes> macro as C110000.

# Contents of VSyncStart.txt

0100 0007

080F 0F01

As mentioned in the previous sections, the Data Type for the VSyncStart signal is 0x01, which means this short packet has its Data ID as 01 and the following two bytes of Packet DATA as 00 00 followed by the ECC of 07.

Therefore, in a sequence, B"VSyncStart.txt" can be written using the C<3 hex bytes> macro as C010000.

Notice that within each text file considered so far, a hexadecimal value 080F 0F01 is mentioned. This is the EoT package, which is used at end of each HS transmission in a short packet. The EoT package has a fixed format with Data ID as 08, Payload Data as 0F0F and ECC of 01.

Therefore, at the end of each C<3 hex bytes> macro defined for the four files, you must add the C<3 hex bytes> macro for the EoT package as C080F0F, as shown in the sequence definition.

# Contents of Video480pHSyncStart.txt

0EA0 0508

1084 1084

1084 1084

1084 1084

.

•

.

1084 1084

FA44 1914

001F 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 6F1D

2100 0012

080F 0F01

The elements of the actual video data in the file 'Video480pHSyncStart.txt' can be divided as follows:

- The header consists of Data ID: 0E followed by a two-byte word counter A005, followed by the ECC for that header data as 08.

- The actual video payload data starts from a hex value of 1084 and ends at a hex value of 1084. Note that the payload data is too long and has been truncated for documentation purpose.

- At the end of the payload, a two byte CRC is added, which is FA44.

- After the checksum, a Blanking packet is added to covey the blanking timing information in this video packet. This Blanking packet consists of the DI byte of 0x19, a two-byte Word Count of 1400, an ECC byte of 1F, a payload of 20 bytes, and a two-byte checksum of 6F1D. This blanking packet enables the HS-LP transition and corresponds to the HFP (Horizontal Front Porch) before the HSyncStart.

- In the end, a short packet in HS mode is generated, which has the HSyncStart data, which allows the HS-LP transition, before the device goes into a low power state.

Looking back at the Video block, the B"Video480pHSyncStart.txt" is replaced by COE"Video480p.txt",BL20,C210000,C080F0F, which indicates that only the actual payload data has been extracted into another text file named Video480p.txt and the rest of the data is appended using the C-Macro to the beginning and to the end of the payload data file. Notice that the Blanking packet with Data ID 0x19, which was part of the initial payload data, has been rewritten using the BL<number of blanking bytes> macros as BL20.

Irrespective of whether you use the B-Macros or the C-Macros, you must ensure that the data is defined in the correct order and you can use the sequence file in either format for waveform generation in the plug-in.

Notice that there has been no change made to the LPInit block of the sequence file, even though the HSyncEnd.txt file is used. This is because even though the HSyncEnd.txt contains hexadecimal data for HS mode, the LPB"filename" macro is used for generating Low Power data specified in the file HSyncEnd.txt, such that the display device is powered on.

To know more about the Data Types required to construct the short or long packets or to define C-Macros in a sequence file, refer to the MIPI Alliance Specification for Display Serial Interface.

#### Understanding a DSI sequence file

The DSI sequence file corresponds to the package structure shown in the image below, which is based on the Non-Burst mode with Sync Pulses:

#### Vsync 858 PCLK = 1716 bytes BLLP-1 BLLP-2 HSE VSA HSS BLLP-1 HSE BLLP-2 **VSE** BLLP-1 HSE BLLP-2 30 **VBP** BLLP-1 HSS BLLP-2 HSE HSS BLLP-1 HSE BLLP-3 Pixel Bytes BLLP-4 BLLP-3 BLLP-4 HSS BLLP-1 HSE Pixel Bytes 525 Lines BLLP-1 BLLP-3 BLLP-4 HSS HSE Pixel Bytes HSS BLLP-1 HSE BLLP-3 Pixel Bytes BLLP-4 480 VACT HSS BLLP-1 HSE BLLP-3 Pixel Bytes BLLP-4 HSS BLLP-1 **HSE** BLLP-3 Pixel Bytes BLLP-4 HSS BLLP-1 HSE BLLP-3 Pixel Bytes BLLP-4 HSS BLLP-1 BLLP-3 BLLP-4 **HSE** Pixel Bytes HSS BLLP-1 HSE BLLP-2 VFP HSS BLLP-1 HSE BLLP-2 Hsync HSA HBP HACT HFP 16 pclk 62 pclk 60 pclk 720 pclk

#### Values in Red text are for a vertical resolution of 480p. Active image size is 720PCLK (Horizontal) x 480 Lines (Vertical).

Figure 7 Block Diagram for Video transmission in Non-Burst mode with Sync Pulses

In general, the way the DVI functions is like the CRT mode. In a video frame of the CRT mode, an electron beam performed several horizontal traces and a vertical trace to begin the next frame. In the current technology, the HSS corresponds to the several horizontal traces whereas VSS corresponds to the vertical trace.

The VSyncStart (VSS) and HSyncStart (HSS) pulse are generated to mark the start of the video frame and define the timings of the device. For a video with resolution 720x480p, there are 720 horizontal active pixels, represented by HACT and 480 vertical active lines, represented by VACT. The device manufacturer provides the information about the horizontal blanking pixels and the vertical blanking lines that must be included to meet the timing and power saving requirements of the device, apart from the video transmission. In this case, a total of 138 horizontal blanking pixels are added to the 720 horizontal active pixels. Also, a total of 45

vertical blanking lines are added to the 480 vertical active lines. These HSync and VSync data is required for proper synchronization of the video data and to achieve proper timing in displaying the video data and is represented by HSyncActive (HSA) and VSyncActive (VSA), respectively. As described earlier, HSS, HSE, VSS and VSE are short packets containing High Speed data and blanking header information. They are part of the HSA and VSA.

Sync events are introduced such that only HSS have to be added. In this case, where Sync pulses are used, Blanking Lines can be added, which may be HS or LP, depending on the timing set between HSS and HSE.

The Horizontal Back Porch (HBP), Horizontal Front Porch (HFP), Vertical Back Porch (VBP), Vertical Front Porch (VFP) are indicated by BLLPs. The Blanking or Low-Power Interval (BLLP) is defined as a period during which video packets such as pixel-stream and sync event packets are not actively transmitted to the peripheral. The BLLP provides for the HS-LP and LP-HS transition when the device is powered on, during the switch to video mode and to save the device's power either in the idle state or just before the start of the video data. In this image, the HBP and HFP are indicated by BLLP-3 and BLLP-4, respectively whereas VBP and VFP are indicated by BLLP-1 and BLLP-2, respectively.

Now, let us consider the example given below of a sequence file for DSI implementation, derived from the video package displayed in the image above.

```

HSFreq: 432.432MBit/s;

```

Blocks:

LPInit: LPB"HSyncEnd.txt",LP11E13728;

HSync: C310000,C080F0F,LP11E12736,C210000,C080F0F,LP11E13728;

VSyncStart: C310000,C080F0F,LP11E12736,C010000,C080F0F,LP11E13728;

VSyncEnd: C310000,C080F0F,LP11E12736,C110000,C080F0F,LP11E13728;

Video:

C310000,C080F0F,LP11E960,C0E"Video480p.txt",BL20,C210000,C080F0F,LP11E 13728:

Sequence:

- 1. LPInit,1;

- 2. HSync,9;

- 3. VSyncStart,1;

- 4. HSync,5;

- 5. VSyncEnd,1;

- 6. HSync,29;

- 7. Video,480;

#### LoopTo 2;

The LPInit block generates the HsyncEnd signal is a low power mode to power on the display device.

To achieve proper synchronization and timing for the video data, the HSync and VSync signals are used. The number of vertical blanking lines and horizontal blanking pixels are provided by the device manufacturer.

The HSync block, which loops over for 9 lines, generates the HSE signal, indicated by C310000,C080F0F before the device switches to low power mode until 12736 HS states are attained. The LP11E12736 corresponds to BLLP-2 on the image. Then, HSS signal is generated, indicated by C210000,C080F0F, after which the device enters into low power mode again until 13728 HS states are attained. The LP11E13728 corresponds to BLLP-1 on the image.

The VSyncStart block, which loops over once, generates the HSE signal followed by LP11E12736 state. Then, VSS signal is generated, indicated by C010000,C080F0F, after which the device enters into low power mode again until 13728 HS states are attained.

The HSync block loops over for 5 lines again before the VSyncEnd block loops over once. The VSyncEnd block generates the HSE signal followed by LP11E12736 state. Then, VSE signal is generated, indicated by C110000,C080F0F, after which the device enters into low power mode again until 13728 HS states are attained.

The HSync block loops over for 29 lines again before the Video block loops over for 480 lines. In the Video block, the HSE signal is generated followed by LP11E960 state. Here, in the duration between the Video line and HSyncEnd, there is a short LP state to allow the device to save power before the video starts. LP11E960, which forms the HBP, allows device to save power before switching to video mode. C0E"Video480p.txt" indicates the header information followed by the active payload data contained in the "Video480p.txt" file. The Video block displays BL20, which forms the HFP, before the HSS is generated again followed by switching into low power mode until 13728 HS states are attained.

Note that BLLP-1 and BLLP-2, that is, LP11E12736 and LP11E13728 are blanking lines. Instead of sending video data, long LP states are generated. The total number of HS states is driven by the E marker, which

means each line has a fixed duration, depending on the data rate. It includes the HS states before the LPE marker is defined and the time taken to switch to the HS mode.

You must always ensure that to define a proper sequence, each block must end with the same HS or LP state to avoid any unexpected loops.

# Calculating HS Data Rate for the DSI sequence

To calculate the minimum HS data rate required to run the sequence, you must be aware of at least the frame rate, the Blanking Lines (HBlank and VBlank) and the device's display resolution, in other words, the pixels per line and lines per frame, which are provided by the device manufacturer. The HS Frequency is the first line in the definition of a sequence file.

For example, let us consider that the device under test has a Frame Rate of 60 Hz and a display resolution of 640 x 480 pixels, where 640 is the horizontal resolution (or the length of each line) and 480 is the vertical resolution (or the number of video lines). The number of header (blanking lines) is given as 45.

1 Calculate the total no. of lines using the equation:

Total Lines = Video Lines + Header (Blanking) lines = 480 + 45 = 525 lines

2 Calculate the Line Rate using the equation:

Line Rate = Frame Rate \* Total Lines = 60 Hz x 525 lines = 31.5 kHz

3 Calculate the No. of pixels per line using the equation:

No. of pixels per line = HBlanking + Horizontal Resolution where, the HBlanking data is given by the device manufacturer. Let us assume 160 HBlanking lines.

Therefore, No. of pixels per line = 160 + 640 = 800 pixels per line.

4 Determine the number of bits required for transmission of the video data. To do so, check the pixel color coding for the Data Type in the video from the device's specification. In this case, the pixel color code is RGB, which uses 24-bits per pixel.

Calculate the total no. of bits per line using the equation:

Total no. of bits per line = Bit-size per pixel \* No. of pixels per line

In this case, Total no. of bits per line = 24 \* 800 = 19.2 kbits per line

5 Calculate the HS Data Rate using the equation:

Data Rate = Line Rate \* Total no. of bits per line

In this case, Data Rate = 31.5 kHz \* 19.2 kbits per line = 604.8 Mbps

2

Therefore, for a VGA mode video with a frame rate of 60 Hz, you must set a data rate of 604.8 Mbps, which you can define as HSFreq in the beginning of the sequence file.

For information on the DSI implementation in the MIPI D-PHY and MIPI C-PHY physical layer and detailed understanding of the protocol layer, refer to the MIPI Alliance Specification for Display Serial Interface.

# 3 Using MIPI D-PHY Editor User Interface

Basic Requirements / 48

Installing Plug-in / 52

Related Documents / 53

Starting the MIPI D-PHY Editor Plug-in / 54

Contacting Keysight Technologies / 56

MIPI D-PHY Editor User Interface / 57

Setting up MIPI D-PHY Editor Parameters / 76

Performing In-System AWG Calibration with Keysight IQ Tools / 99

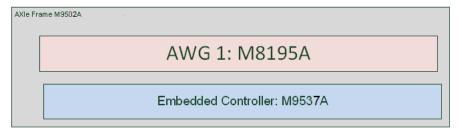

New Sequences in MIPI D-PHY 2.1 / 114

# Basic Requirements

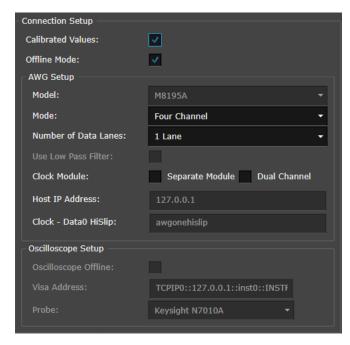

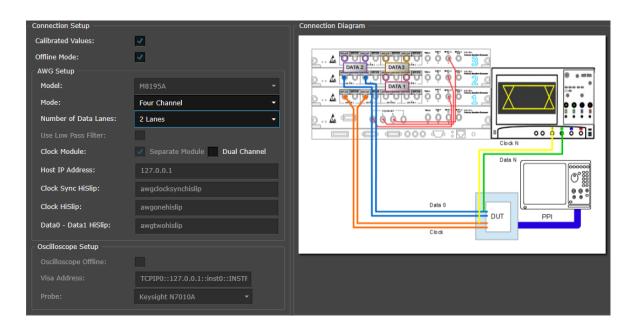

Hardware Setup using M8195A AWG Module

#### Single-lane Setup

The required hardware setup for single-lane using M8195A module are following:

- One M8195A module

- · An Embedded Controller (such as M9537A) or an external PC

- M9502A AXIe 2-Slot Chassis

- · An Infiniium or SCPI compatible oscilloscope

- · LAN or GPIB adapter

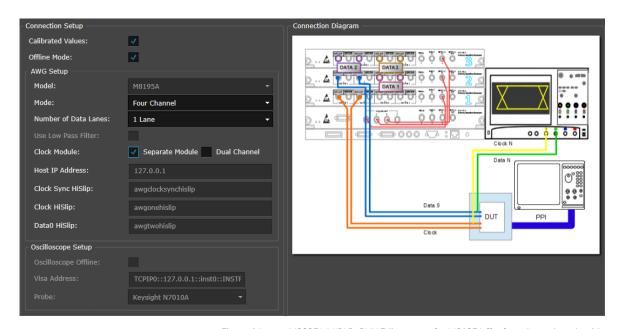

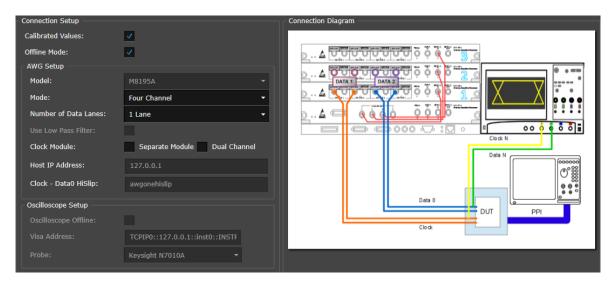

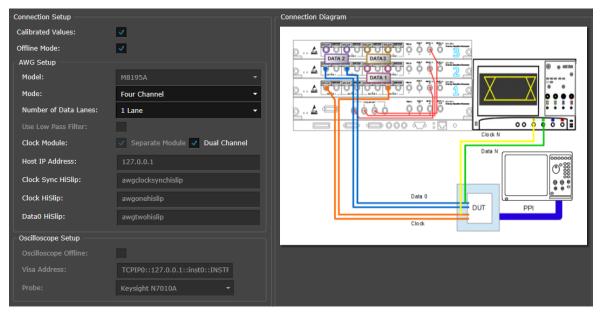

For hardware setup of a single lane (either Dual Channel or Four Channel mode):

1 Insert an M8195A and an Embedded Controller in the 2 slot frame AXIe chassis as shown in Figure 8.

Figure 8 Hardware setup for Single-lane with module M8195A

- 2 M9502A contains only two slots. The Embedded Controller must be installed in the slot 1 of the AXIe chassis otherwise, it will not be able to connect to the internal PCIe interface of the frame.

- 3 The slot 2 contains the M8195A AWG module.

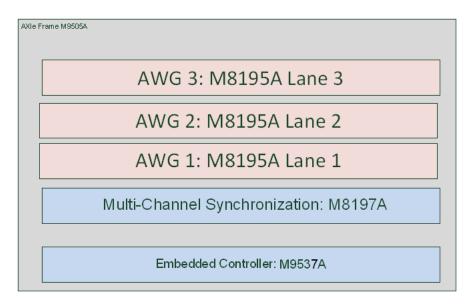

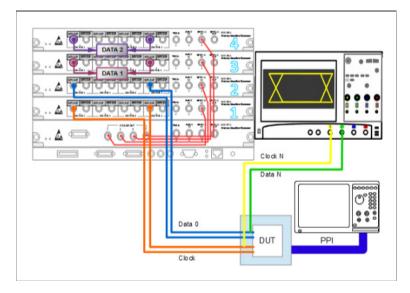

### Multi-lane Setup

Following hardware setup is required for multi-lane:

- Two or three M8195A AWG modules to enable the multi-lane support (two data lanes in Dual Channel mode and up to four data lanes in Four Channel mode)

- One M8197A module to synchronize multi M8195A modules

- M9505A AXIe 5-Slot Chassis

- for two lane structure 2 slots for two M8195A modules, 1 slot for one M8197A module and 1 slot for embedded controller (optional)

- for three lane structure 3 slots for three M8195A modules, 1 slot for one M8197A module and 1 slot for embedded controller (optional)

# NOTE

M8197A module is used to synchronize M8195A modules (Lane 1, Lane 2, Lane 3 and Lane 4). However, if you are using only single M8195A module (Lane 1), then M8197A is not required.

Consider Figure 9 to achieve up to three lane hardware setup:

1 Put three M8195A and one M8197A in the 5 slot frame AXIe chassis.

Figure 9 Hardware setup with two or three lane M8195A

- 2 The modules should be arranged inside a 5 slot chassis in the following order:

- Slot 1: M8197A (Used for synchronization)

- Slot 2: M8195A (Used for lane 1)

- Slot 3: M8195A (Used for lane 2)

Slot 4: M8195A (Used for lane 3)

# NOTE

You can also use an embedded controller for M8070B and/or the AWG SFPs or a remote PC as an external controller. The modules for multi-lane M8195A is also de-skewed itself.

# Software Requirements

To install the MIPI D-PHY Editor plug-in, the M8070B software (version S6.0.100.2 or later) is required. You can download the software from the following link:

http://www.keysight.com/find/M8070B

# License Requirements

The MIPI D-PHY Editor plug-in is a licensed feature. To enable it, Table 2 shows the required licenses:

Table 2 License required for MIPI D-PHY Editor plug-in

| P/N       | License | Description                                                                                                                       |

|-----------|---------|-----------------------------------------------------------------------------------------------------------------------------------|

| M8085DE1A | -1TP    | MIPI D-PHY 2.1 Editor for M819xA AWG, Transportable,<br>Perpetual License                                                         |

|           | -1NP    | MIPI D-PHY 2.1 Editor for M819xA AWG, Network/Floating,<br>Perpetual License                                                      |

|           | -TRL    | MIPI D-PHY 2.1 Editor for M819xA AWG, 30 Day Trial License                                                                        |

| M8085DC1A | -1TP    | MIPI D-PHY 2.1 Calibration, Conformance and<br>Characterization Procedures for M819xA AWG, Transportable,<br>Perpetual License    |

|           | -1NP    | MIPI D-PHY 2.1 Calibration, Conformance and<br>Characterization Procedures for M819xA AWG,<br>Network/Floating, Perpetual License |

|           | -TRL    | MIPI D-PHY 2.1 Calibration, Conformance and<br>Characterization Procedures for M819xA AWG, 30 Day Trial<br>License                |

| P/N       | License | Description                                                                                                                                                                       |

|-----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M8085DUEA | -1TP    | Upgrade MIPI D-PHY Editor from M8085A-DT1 to D-PHY 2.1,<br>Transportable, Perpetual License                                                                                       |

|           | -1NP    | Upgrade MIPI D-PHY Editor from M8085A-DN1 to D-PHY 2.1,<br>Network/Floating, Perpetual License                                                                                    |

| M8085DUCA | -1TP    | Upgrade MIPI D-PHY Editor plus Calibration, Conformance<br>and Characterization Procedures from M8085A-DT1 and<br>M8085A-DTA to D-PHY 2.1, Transportable, Perpetual License       |

|           | -1NP    | Upgrade MIPI D-PHY Editor plus Calibration, Conformance<br>and Characterization Procedures from M8085A-DN1 and<br>M8085A-DNA to D-PHY 2.1, Network/Floating, Perpetual<br>License |

| N5990A    | -010    | Test Sequencer                                                                                                                                                                    |

# Installing Plug-in

The MIPI D-PHY Editor plug-in must be installed separately other than the M8070B system software.

Please make sure that the system should already have M8070B (version 6.0.100.2 or later) software installed on it.

M8195A SFP should be installed from V3.6.0.0 and M8197A SFP should be installed from V3.6.0.0.

The installer for the MIPI D-PHY Editor plug-in is available either on CD or you may download it from the from the following Keysight web-page: www.keysight.com/find/m8085a.

For details on how to install the MIPI D-PHY Editor plug-in, refer to the Keysight M8085A Plugins for MIPI Receiver Test Solutions Installation Guide.

# Related Documents

The plug-ins are installed separately from the plug-in manager.

For details on how to use the **Plug-in Manager** to install, uninstall and update the **M8085A** plug-in, refer to the *Installing M8085A Plugins for MIPI Receiver Test Solutions* section in *Keysight M8000 Series of BER Test Solutions Plugins for M8070B System Software Getting Started Guide*.

For M8070B plug-ins related documents, click **Start** > **Keysight M8070B** > **Keysight M8070B Documentation**.

# Starting the MIPI D-PHY Editor Plug-in

To access the installed MIPI D-PHY Editor plug-in through the M8070B system software:

- 1 Click Start > Keysight M8070B. The user interface for the M8070B system software appears.

- 2 From the M8070B user interface menu, click **Application** to view the list of all installed plug-ins.

- 3 Select the MIPI D-PHY Editor plug-in.

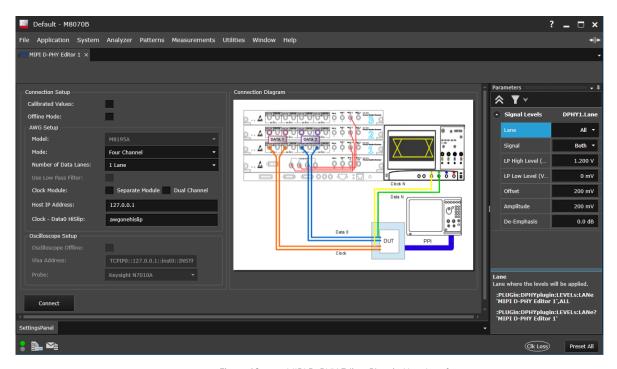

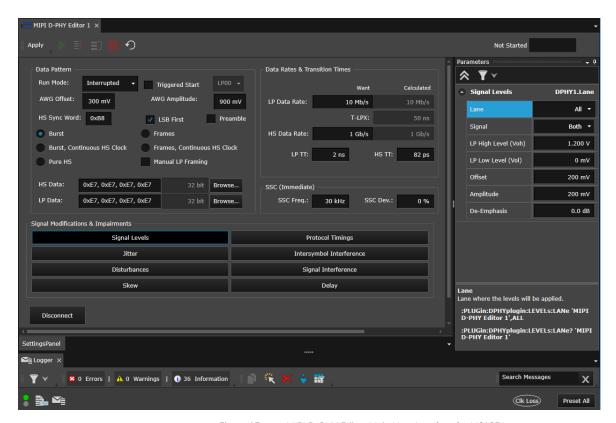

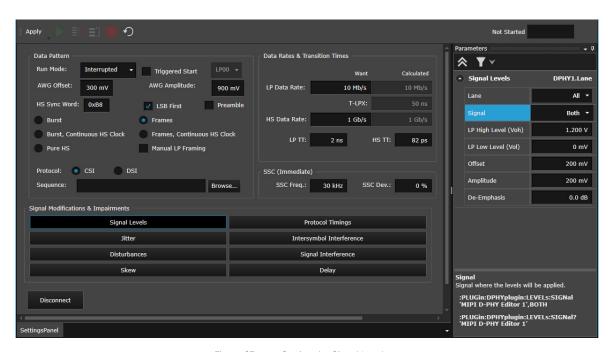

- 4 The MIPI D-PHY Editor user interface appears as shown in Figure 10.

Figure 10 MIPI D-PHY Editor Plug-in User Interface

NOTE

If you are unable to see the MIPI D-PHY Editor option in the **Menu Bar > Applications**, you must have to install it separately. Ensure that you have a valid license to install the software.

Currently, the shortcut for Keysight M8085A plug-ins is not auto-generated during installation.

To manually create a shortcut to the Keysight M8070B software on your desktop to access the M8085A plug-ins, perform the following steps:

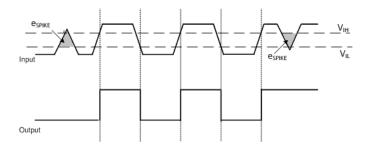

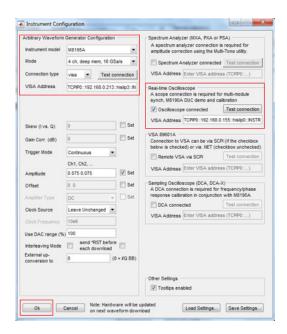

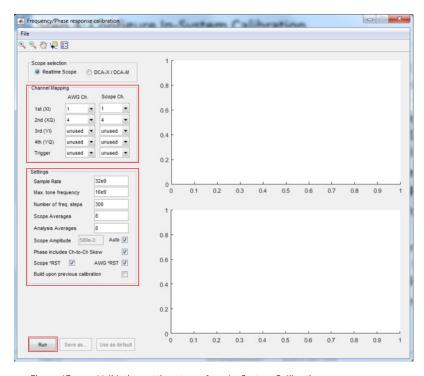

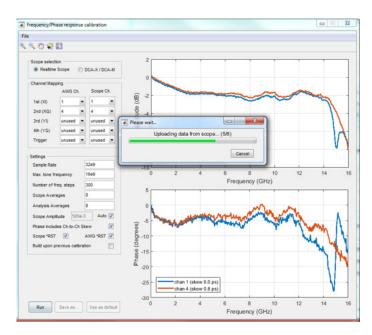

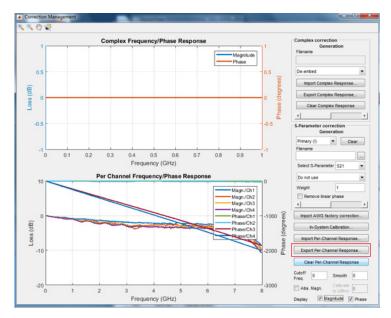

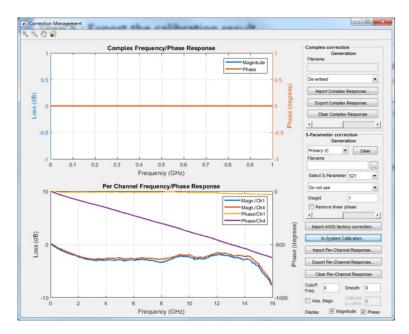

- 1 Navigate to C:\Program Files\Keysight\M8070B\bin folder on your machine.