The PathWave ADS Memory Designer Bundle includes the following key features and capabilities:

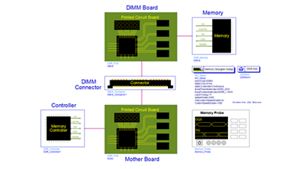

- Dramatically reduce setup time with new components for easy setup of controller, PCB, connectors, terminations and memory

- IBIS files can be applied ‘per device’ giving faster setup and parameterization of settings for groups of signals

- Automated wiring connections, utilizing DDR Signal IDs found in the layout design

- DDR Bus simulator to characterize signal integrity, capturing margin-to-mask tests down to ultra-low BERs

- New Memory Probe to set up measurements by group, with intelligent selection of signal references

- New strobed-eye diagrams and skew measurements

- Automated DDR4 Compliance Test suite and report generation, utilizing Keysight’s industry-recognized DDR4 measurement science

- Support for DDR5 and LPDDR5 with an Bit-by-Bit simulation, using IBIS-AMI enhanced for the requirements of single-ended DDR signaling

- SIPro and PIPro EM analysis – for fast and accurate electromagnetic extraction of signal nets and power/ground nets

- Capable of Pre-Layout (Via Designer and Controlled Impedance Line Designer) and Post-Layout analysis, for Memory and SerDes designs alike

For a hardware designer working on memory systems, they must contend with both shrinking timing and voltage margins, and a complex list of compliance measurements to ensure reliable operation. As we move to DDR4 and now into DDR5, random jitter, crosstalk and equalization become much more critical. The designer needs to have confidence they can optimize the channel design and pass the Receiver Mask Tests at ultra-low Bit Error Rates (BERs). Keysight’s new PathWave ADS Memory Designer workflow minimizes the engineering effort required to setup, extract EM models, simulate the buses, and perform compliance testing. Offering a unique capability to use the same measurement science for both simulation and hardware verification stages, finally simulation to measurement comparison is made easy.

Predictive. Productive. Insightful.

The ADS Memory Designer Bundle consists of ADS Core, TransConv, Channel, IT, Layout, SIPro, PIPro, and Memory Designer as shown in the table below.

Functionality in this Bundle

| Model Number |

Name |

Description |

|---|

| W2200BP |

ADS Core |

Provides essential RF and microwave design capabilities in a highly productive enterprise schematic design environment. Fast linear simulation, comprehensive filter and passive circuit synthesis. |

| W2302EP |

Transient Convolution and Channel Simulation Element |

Advanced time-domain Element that includes Transient Simulator (SPICE transient analysis including HSPICE and Spectre compatibility modes), IBIS Model Library, Convolution Simulator (creates time-domain models from frequency domain data), Channel Simulator (includes bit-by-bit and statistical modes, eye diagrams and BER contours, IBIS AMI). |

| W2307EP |

Interconnect Toolbox Element |

The Interconnect Toolbox Element enables you to optimize your PCB stack up and design transmission line geometry. It also provides a high accuracy via design simulator which helps you to design a parameterized, impedance-matched via transition (single-ended and differential). |

| W2321EP |

Layout Element |

Comprehensive physical design environment specifically geared for high-frequency circuit development, including artwork import/export for ODB++, DXF, Gerber/drill, IGES and GDS-II formats. |

| W2360EP |

SIPro Signal Integrity EM Analysis Element |

SIPro provides signal integrity (SI) analysis of complex high-speed PCBs, enabling you to characterize loss and coupling of signal nets, and ultimately extract an EM-accurate model that can be used in the ADS Transient and Channel Simulators. |

| W2359EP |

PIPro Power Integrity EM Analysis Element |

PIPro provides complete power integrity (PI) analysis of your power distribution network (PDN). Simulation engines include DC IR drop analysis, Thermal and Electro-Thermal DC analysis, PDN AC impedance analysis, Bill of Materials optimization for decoupling capacitors, and finally power plane resonance analysis. |

| W2393EP |

Memory Designer Element |

The Memory Designer Element includes Memory Designer workflow and DDR Bus Simulator. |