What are you looking for?

GoldenGate 2011.10 (4.6) Product Release

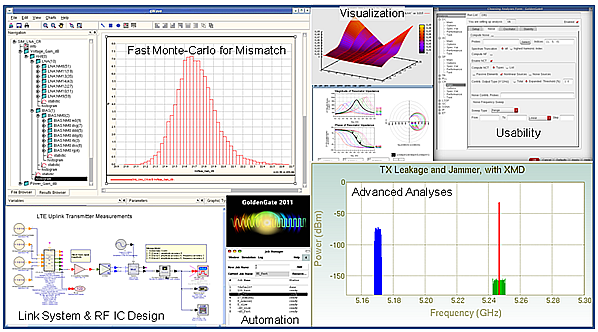

Highlights

Updates to Key Design Analyses in GoldenGate 2011.10:

- Performance Enhancements — Extends Keysight’s RF performance leadership with Carrier Analysis improvements that deliver significantly better performance on multicore CPUs and also better scalability. The Carrier Noise and SSNA Noise analyses performance has also been dramatically improved.

- Fast Yield Contributor — Improve yield by optimizing only what really matters. Determine device, circuit and block yield contributions at any stage of the RFIC design flow. New analyses have been added for RF and Analog/Mixed-Signal designers including DC, and AC and Oscillator analysis.

- Fast Circuit Envelope Analysis — Accelerate RF functional path simulations an order of magnitude or more with broader support for RFIC centric source configurations for models including memory effects.

- Carrier Analysis Based Large Signal Stability — Analyze the stability of oscillators and driven RF circuits including s-parameter blocks with large signal black box Nyquist and Eigenvalue stability.

- Noise Analysis in Transient — Allow noise analysis for non-periodic time-domain simulations.

- Cosimulation with SystemVue (for Early Access users ONLY) — Support cosimulation with SystemVue 2011.10 including fast envelope modeling export to SystemVue.

- Specialized Applications — Reduce the frustration of simulating crystal oscillators with GoldenGate’s enhanced crystal oscillator convergence option.

GoldenGate 2011.10 Improvements in Design Verification:

- Keysight X-parameters* Support — Enhance RF design verification with innovative technology.

- Fast Mismatch Analysis — Dramatically accelerate the block and functional path verification that RFIC designers perform every day without loss of accuracy including new support for Cadence corners tool.

- RF Passive Component Library Updates — Simulate more of your design by including RF package and board effects using the updated adslib for GoldenGate library which now includes delay-defined transmission lines and Philips-TU Delft standard/user-defined bondwire models.

Improvements in Usability:

- New Analysis, Environment, Options and Results GUI — Improve productivity and ease the configuration of RF analyses and environment/options selections with GoldenGate’s new tree/tabbed GUI for Cadence Analog Design Environment.

For Existing Users:

- GoldenGate 2011.10 Release Notes (login required)

Description

GoldenGate is the most trusted simulation, verification and analysis solution available for highly integrated RF circuit design. Its unique simulation algorithms are optimized for the challenging demands of today's complex RF circuit design, enabling full characterization of complete transceivers prior to tape-out. GoldenGate is part of Keysight’s RFIC simulation, analysis and verification solution that also includes Momentum for 3-D planar electromagnetic simulation, Ptolemy/SystemVue Wireless Test Benches for system level verification, and the Advanced Design System (ADS) Data Display for advanced data analysis. This suite links the RF system, subsystem, and component-level design and analysis as part of a unique and comprehensive RFIC design flow. GoldenGate is fully compatible with Cadence IC5 and IC6 platforms.

Note: GoldenGate 2011.10 is a major product release that includes all 4.6.x versions of GoldenGate.

GoldenGate 2011.10 delivers improvements for just about every important aspect of RFIC design in advanced silicon and CMOS technology nodes. It delivers major enhancements in the key analyses and verification flows that designers need not only to improve the performance and yield of their RFICs, but also their productivity.

Approaches to Performance Enhancement

While there are various approaches for delivering performance enhancements for RF simulation, Keysight’s approach has been to provide a continuous incremental stream of performance and memory improvements over the life of the GoldenGate product. While various releases focus on improving the performance of different simulation techniques, the overall goal is to continue to keep the ball moving forward. On average, GoldenGate has doubled the RF simulation performance each year on circuits our customers care most about, even as they move their RFICs into 65nm process technologies and below. Of course, we deliver this without a loss of accuracy or compatibility. As such, GoldenGate 2012 stays true to its heritage as the highest performance, most robust and trusted RF design and verification solution for complex RFICs in the industry.

New Fast Mismatch Analyses for Analog and RF Designers

While process centric Monte-Carlo analysis plays a role in analyzing large scale or global variation effects on circuit performance, Mismatch analysis has typically been the workhorse for understanding small scale or local effects on device behavior. Since it’s normal to run mismatch analysis at every corner for block level signoff, a significant amount of simulation time, computational resources, and simulator licenses are consumed during this effort. Keysight’s Fast Yield and Mismatch technology was originally developed to address this part of the RF design flow by reducing the simulation cost in terms of time, licenses, and hardware availability. With GoldenGate 2011, this solution was extended to non-RF or traditionally analog analyses. Now the whole design team can take advantage of this unique solution.

Innovations in EDA: A Practical Approach to Verifying RFICs with Fast Mismatch Analysis Webcast (no longer available).

Fast Circuit Envelope Analysis

As each new wireless standard emerges, the complexity of the signal structure, modulation and band compatibility requirements have been mirrored in the type and scope of the performance verification that is needed. For many, multi-tone analysis may not go far enough in capturing the behavior of their circuits and may even be misleading or ineffective in modeling certain effects. As such, circuit envelope analysis has emerged as a useful technique for understanding the behavior of RF circuits with modulated signals. However, for large scale RFICs, complete functional path analysis may not be practical in the presence of parasitics or when including other necessary but non-RF circuits. To overcome this, Keysight pioneered the use of Fast Circuit Envelope techniques to accurately model the nonlinear behavior of these circuits including in-band and out-of-band memory effects for use in simulation to accelerate their analysis.

Innovations in EDA: Memory Effects in RF Circuits Webcast (no longer available).

Comprehensive Wireless Test Benches

Wireless communication systems continue getting more complicated with the release of each new standard. Systems engineers and RF IC designers need to collaborate more than ever on specifications driven verification. Keysight is uniquely positioned to leverage the power of Communications Systems and RF circuit simulators together with a comprehensive library of standards based wireless verification IP to accelerate the validation of complex RFICs at both the system and circuit level. Based on links between Ptolemy and GoldenGate, this approach allows the Systems Engineer to use their expertise to configure and package wireless verification test bench libraries for the RFIC Designer to use in a manner appropriate for IC level design.

Understanding Cross Modulation Effects in a Full Duplex LTE Transceiver or Innovations in EDA: Memory Effects in RF Circuits Webcast (no longer available)..

Looking for another version? View other GoldenGate Product Versions.

* "X-parameters" is a trademark of Keysight Technologies, Inc. The X-parameter format and underlying equations are open and documented. For more information click here.