Pathwave FPGA

# M8132A FSP Documentation

#### Notice

#### © Keysight Technologies, Inc. 2021

1400 Fountaingrove Pkwy., Santa Rosa, CA 95403-1738, United States

All rights reserved.

No part of this documentation may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies, Inc. as governed by United States and international copyright laws.

#### Restricted Rights Legend

If software is for use in the performance of a U.S. Government prime contract or subcontract, Software is delivered and licensed as "Commercial computer software" as defined in DFAR 252.227-7014 (June 1995), or as a "commercial item" as defined in FAR 2.101(a) or as "Restricted computer software" as defined in FAR 52.227-19 (June 1987) or any equivalent agency regulation or contract clause.

Use, duplication or disclosure of Software is subject to Keysight Technologies' standard commercial license terms, and non-DOD Departments and Agencies of the U.S. Government will receive no greater than Restricted Rights as defined in FAR 52.227-19(c)(1-2) (June 1987). U.S. Government users will receive no greater than Limited Rights as defined in FAR 52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2) (November 1995), as applicable in any technical data.

### Table of Contents

| Installation Requirements                              | 7  |

|--------------------------------------------------------|----|

| Overview                                               | 8  |

| Scope                                                  | 9  |

| Available FPGA Features and Resources                  | 10 |

| Available Configurations                               |    |

| Port Mapping                                           |    |

| FPGA Configurable Region Interfaces                    | 14 |

| ODI - Optical Data Interface                           |    |

| ODI Resets                                             |    |

| ODI Resets                                             |    |

| ODI Stat tup reset                                     |    |

| ODI Per Channel Flow Control                           |    |

| ODI Clock                                              |    |

| 10Gbe Ethernet Interface                               |    |

| 10Gbe Ethernet Resets                                  |    |

| 10GbE Ethernet Receive Status                          |    |

| DPU2DPU                                                |    |

| DPU2DPU Resets                                         |    |

| DPU2DPU Receive Status                                 |    |

| Register Access                                        |    |

| Register Reset                                         |    |

| Register Clock                                         |    |

| <del>-</del>                                           |    |

| Memory Mapped DMA Access                               |    |

| Clock 400M                                             |    |

| 400M Reset                                             |    |

| Clock 500M                                             |    |

| 500M Reset                                             |    |

| Sync Puse                                              | 33 |

| GP_Trigger_IN                                          | 34 |

| GP_Trigger_OUT                                         | 34 |

| HS_TRIGGER_OUT                                         |    |

| Gearbox Clear                                          |    |

| Boundary Scan                                          |    |

| -                                                      |    |

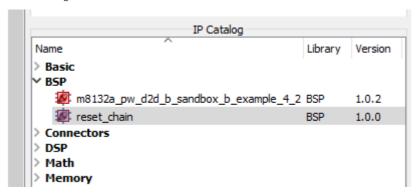

| BSP IP Repository                                      |    |

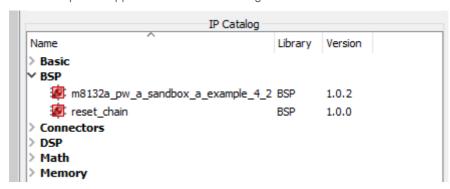

| FPGA A Sandbox 1 Configuration A                       |    |

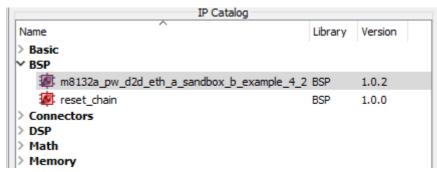

| FPGA A Sandbox 1 Configuration B                       |    |

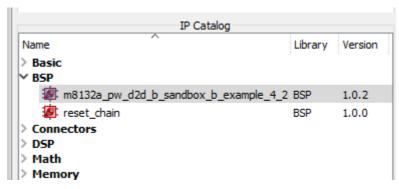

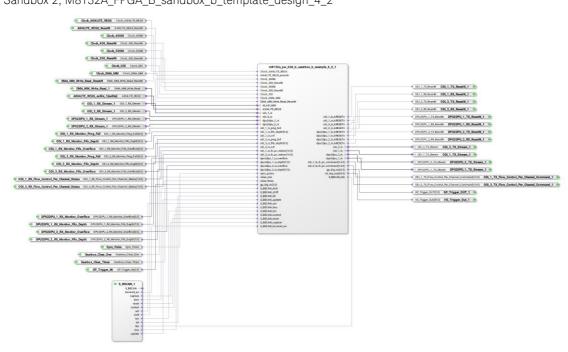

| FPGA B Sandbox 2 Configuration B                       | 42 |

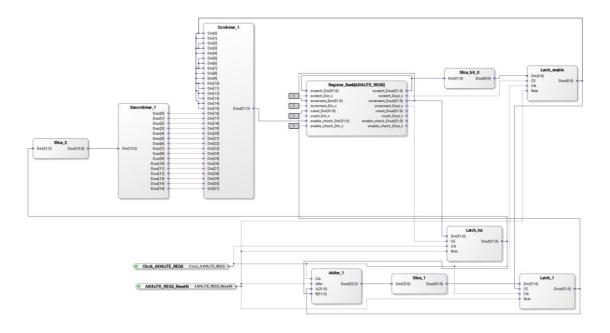

| Common                                                 | 44 |

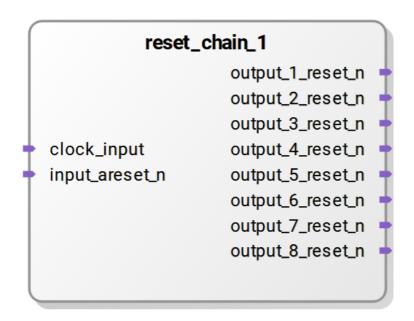

| reset_chain                                            | 44 |

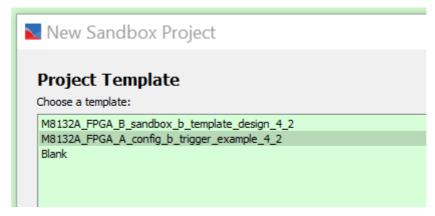

| Example Designs                                        | 45 |

| M8132A Template Example Design Description             |    |

| GeneralGeneral example besign bescription              |    |

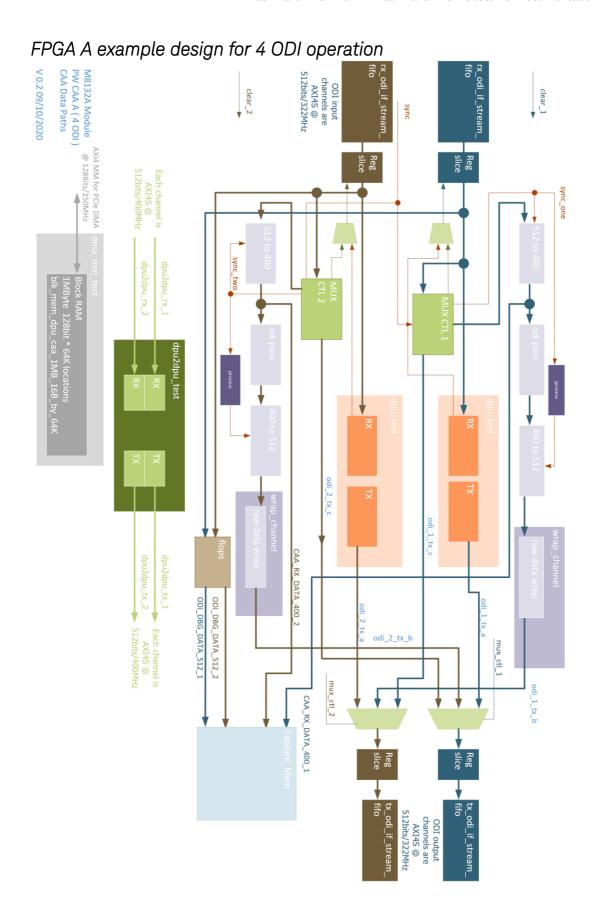

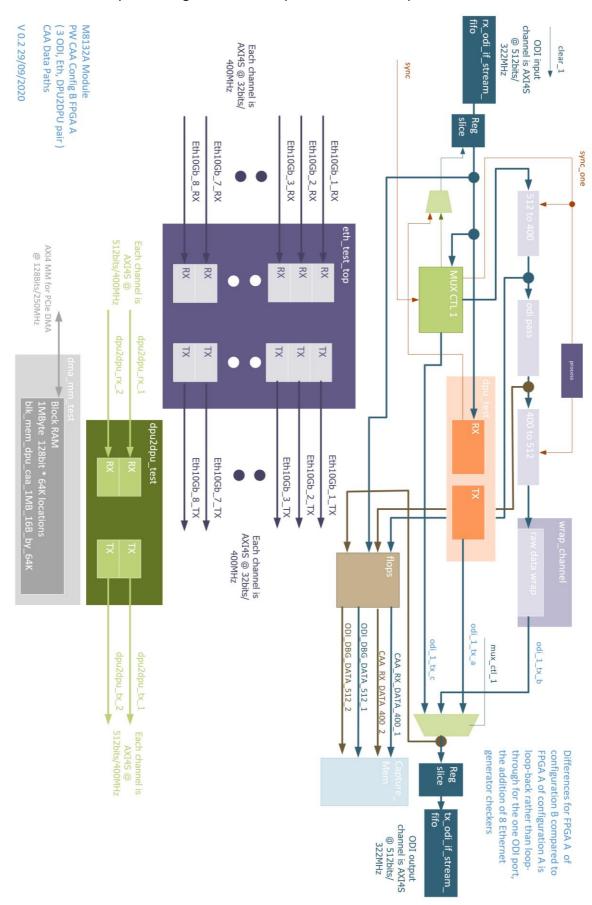

| FPGA A example design for 4 ODI operation              |    |

| FPGA A example design for 3 ODI plus 8 10GbE operation |    |

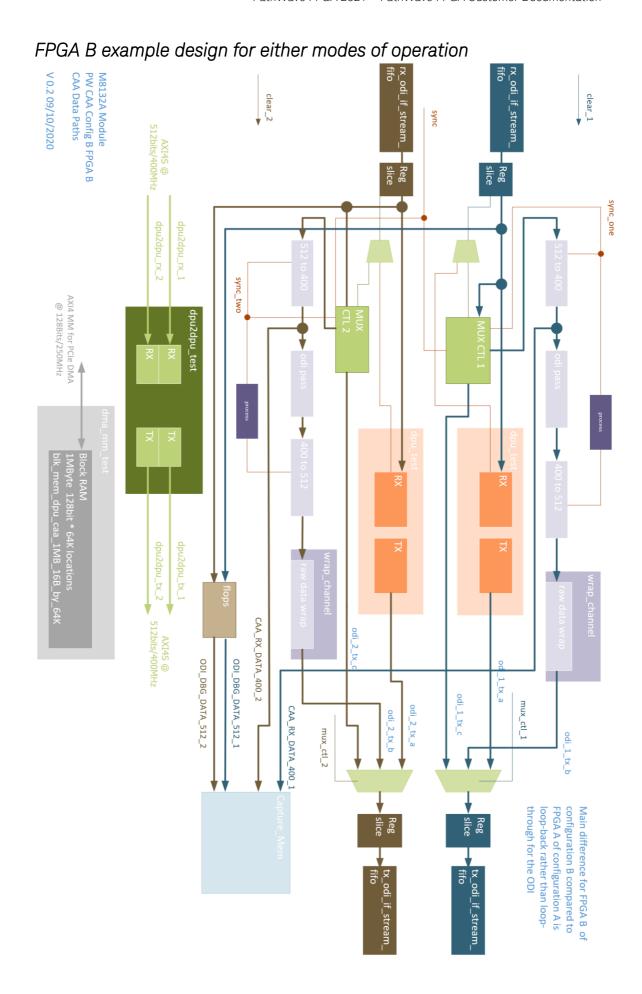

| FPGA B example design for either modes of operation    |    |

| ODI                                                    |    |

| General                                                |    |

| Basic Operation                                        |    |

| A Note on ODI over AXI4S                               |    |

| A Note on the 400bit bus operation                     |    |

| The 4 ODI FPGA A Example Design ODI features           |    |

| The 3 ODI FPGA A Example Design Got reatures           |    |

| The FPGA B Example Design features                     |    |

| Source Code                                            |    |

| Memory Map                                                            |          |

|-----------------------------------------------------------------------|----------|

| ODI Test Control & Status                                             | 57       |

| ODI Mux Control Ctl/Stat                                              |          |

| ODI Pass Through Ctl/Stat                                             | 58       |

| Capture Memory                                                        | 59       |

| Register Descriptions                                                 | 59       |

| Test Packet Generation Registers                                      |          |

| Interlaken Channel                                                    |          |

| Transmit General                                                      |          |

| RX Status                                                             |          |

| Receive General                                                       |          |

| RX Active Clocks Lower                                                |          |

| RX Active Clocks Upper                                                |          |

| RX Total Clocks Lower                                                 |          |

| RX Total Clocks Upper                                                 |          |

| Segment Errors                                                        |          |

| Core Clock Rate                                                       |          |

| TX Clock Crossing fifo depth                                          |          |

| TX Clock Crossing fifo depth max                                      |          |

| RX Clock Crossing fifo depth                                          |          |

| RX Clock Crossing fifo depth max                                      |          |

| RX Flow Control fifo depth                                            |          |

| RX Flow Control fifo depth max                                        |          |

| ODI Pass Through Ctl/Stat                                             |          |

| General                                                               |          |

| DPU BB ODI CHANNEL                                                    |          |

|                                                                       |          |

| DPU_BB_ODI_PACKET_LENGTH                                              |          |

| DPU_BB_CONTROL                                                        |          |

| DPU_BB_STATUS                                                         |          |

| General                                                               |          |

| DPU_BB_DATA_COUNT                                                     |          |

| DPU_BB_CORE_CLOCK_RATE                                                |          |

| ODI Mux Control Ctl/Stat                                              |          |

| DPU_MUX_SELECT                                                        |          |

| Valid Combinations for in 2 and out 4                                 |          |

| Valid Combinations for in 4 and out 2                                 |          |

| Valid Combinations for FPGA B or FPGA A in 3 ODI plus 10GbE operation |          |

| NOTES:                                                                |          |

| DPU_MUX_CONTROL                                                       |          |

| DPU_MUX_STATUS                                                        |          |

| DPU_MUX_DATA_COUNT_LOWER                                              | 71       |

| DPU_MUX_DATA_COUNT_UPPER                                              |          |

| DPU_MUX_TX_FIFO_DEPTH                                                 |          |

| DPU_MUX_RX_FIFO_DEPTH                                                 | 71       |

| DPU_MUX_STARTUP_DEPTH                                                 | 71       |

| DPU_MUX_EMPTY_DEPTH                                                   | 71       |

| DPU_MUX_ODI_PACKET_LENGTH                                             | 71       |

| Capture Control                                                       | 72       |

| General                                                               | 72       |

| Capture Control                                                       | 72       |

| Format                                                                | 72       |

| Capture Data Vectors                                                  | 72       |

| Read Request Addr                                                     |          |

| StartAddr and Offset                                                  |          |

| Read Request Samples                                                  |          |

| Read Request Control                                                  |          |

| Read Data                                                             |          |

| Abort                                                                 |          |

| Capture Memory Status Register                                        |          |

| DDC Access Control Register                                           |          |

| ReadData(0 - F) Read only                                             |          |

| ReadData() - 17 Read only                                             |          |

| ReadData0                                                             | 75<br>75 |

| ReadData2                                                                         |       |

|-----------------------------------------------------------------------------------|-------|

| ReadData3                                                                         | 75    |

| ReadData4                                                                         | 75    |

| ReadData5                                                                         |       |

| ReadData6                                                                         |       |

| ReadData7                                                                         |       |

| ReadData8                                                                         |       |

| ReadData9                                                                         |       |

| ReadDataA                                                                         |       |

| ReadDataB                                                                         |       |

| ReadDataC                                                                         |       |

| ReadDataD                                                                         |       |

| ReadDataE                                                                         |       |

| ReadDataF                                                                         | -     |

| General                                                                           |       |

| Ethernet                                                                          |       |

| ET Control                                                                        |       |

| ET TX AddressET TX Length                                                         |       |

| ET TX IPG                                                                         |       |

| ET TX Repeats                                                                     |       |

| ET RX Address                                                                     |       |

| ET RX Length                                                                      |       |

| ET Rx Errored Count                                                               |       |

| ET Rx Length Errored Count                                                        |       |

| ET Rx Data Errored Count                                                          |       |

| ET Tx Ack Count                                                                   |       |

| ET RX Ack Count                                                                   |       |

| Ethernet Test Operation and procedures                                            |       |

| Addresses                                                                         |       |

| Source Address Override                                                           |       |

| Examples                                                                          | 83    |

| Loopback Dongle                                                                   | 83    |

| Breakout cable                                                                    |       |

| DPU2DPU                                                                           | 87    |

| General                                                                           |       |

| A note on the DPU2DPU AXI4S stream                                                |       |

| Memory Map                                                                        |       |

| DPU2DPU Test Control & Status                                                     |       |

| Register Descriptions                                                             |       |

| DPU2DPU Test Packet Generation Registers                                          | 89    |

| Test Benches                                                                      |       |

| m8132a_pw_a_sandbox_a_example_4_2_tb.vhd                                          |       |

| m8132a_pw_d2d_b_sandbox_b_example_4_2_tb.vhd                                      |       |

| m8132a_pw_d2d_eth_a_sandbox_b_example_4_2_tb.vhd                                  | 94    |

| dpu_caa_pw_example_4_2_data_512_capture_tb.vhdcapture_mem_top_tb.vhd              | 94    |

| dpu_caa_pw_example_4_2_ethernet_tb.vhd                                            |       |

| dpu_caa_pw_example_4_2_ethernet_tb.vnddpu_caa_pw_example_4_2_data_400_path_tb.vhd |       |

| dpu_caa_pw_example_4_2_data_400_loopback_tb.vhd                                   |       |

| dpu_caa_pw_b_cxample_4_2_data_400_loopback_tb.vhd                                 |       |

| dpu_caa_pw_a_example_4_2_dpu2dpu_tb.vhd                                           |       |

| dpu_caa_pw_d2d_b_example_4_2_dpu2dpu_tb.vhd                                       |       |

| dpu_caa_pw_example_4_2_dpu2dpu_tb.vhd                                             |       |

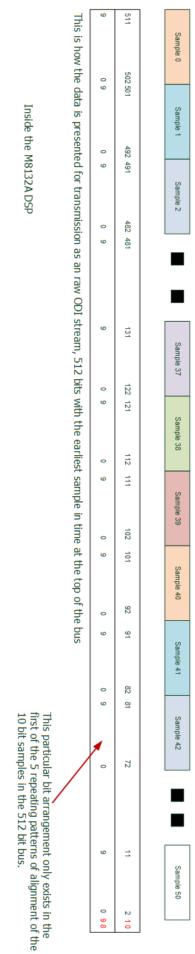

| Bus Widths and Sample Ordering                                                    |       |

| 400Bit to 512Bit Gearbox and ODI Transmission                                     |       |

| 512Bit and ODI Transmission                                                       |       |

| M8132A Register Example                                                           |       |

| M8132A Trigger Out Example                                                        |       |

| 32GS/s TX/RX ODI Connection                                                       |       |

| 0200/ 0 1/// N/\                                                                  | 1   4 |

## Installation Requirements

In addition to the PathWave FPGA system requirements, this FSP requires the following software to allow the output products to be used with the M8132A Module

| Vendor   | Software                                                                                                    | Release<br>Supported  | May work, but not supported | Release<br>Explicitly not-<br>supported |

|----------|-------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------|-----------------------------------------|

| Keysight | M8131A/M8132A SFP Drivers, programming libraries and Software Front Panel for the following modules: M8132A | 4.1.0.0 to<br>4.2.X.X | NA                          | Older versions                          |

| Xilinx   | Vivado                                                                                                      | 2019.2                | 2020.X,<br>2021.X           | Versions older than 2019.2              |

#### Overview

The M8132A is a high performance DSP module, which incorporates 160Gb/s optical IO using ODI, and as of release 4.1 has the option to replace one of the ODI links with eight 10GbE Optical Links compatible with IEEE 802.3-2012 10GBASE-SR optical interfaces.

The M8132A data sheet outlines the performance specifications for the M8132A and should be available at:

#### http://www.kevsiaht.com/find/M8132A

The M8132A User's Guide provides information on the modules base operation, and information on the example software that operates with the example design templates provided with the FSP

It is available from the drop down menu "Help"  $\rightarrow$  "User Guide" from the soft front panel of the M8132A, or from the start menu folder on the machine with the M8131A/M8132A main install: Keysight M8131  $\rightarrow$  Keysight M8131 Documentation. Then open and "M8132A User's Guide.pdf"

#### Scope

This document is a technical reference for the M8132A 640 Gb/s Digital Signal Processor Module, with regard to the configurable regions of the M8132A FPGAs. The FPGA configuration regions utilize Xilinx FPGA partial reconfiguration technology to allow customers to design and configure defined sections of the M8132A FPGAs without the need to power down or reboot the M8132A or host computer, respectively.

#### Available FPGA Features and Resources

The M8132A is purchased as a 4 channel processing system.

The M8132A supports two customer accessible areas (CAA), each supporting 2 main IO channels, and as of release 4.1, two inter-FPGA bi-directional links, and the option to replace one of the ODI channels with 8 10GbE links.

There is one CAA per FPGA, the FPGA are both xcvu9p-flga2577-2L-e.

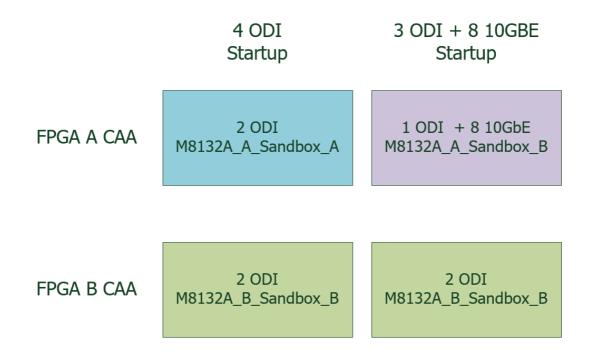

There are two different startup options for the M8132A Soft Front Panel (SFP), which load up either one of two possible pairs of static regions with default partial Customer Accessible Area contents.

See the M8132A User's Guide Chapter 3 section dealing with Command Line Arguments for information on how to start the SFP with the eight 10GbE ports instead of the 4th ODI port.

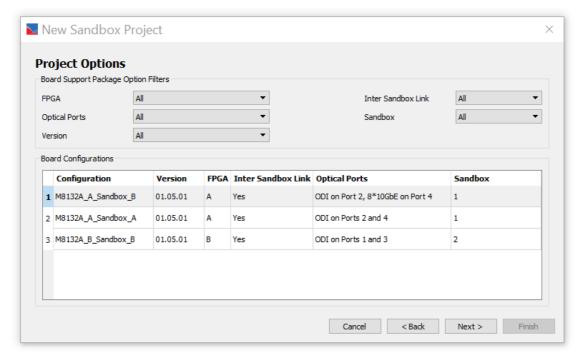

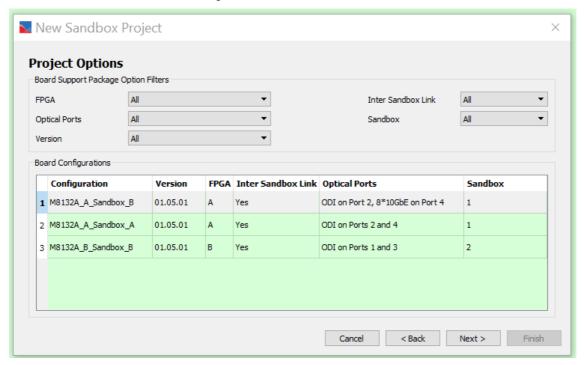

There are three configurations supplied with the FPGA Support Package (FSP) that allow the user to build partial bit-streams suitable for the particular startup static regions in use.

The "A" configuration for FPGA A supports the 4 ODI IO operation, the "B" configuration for FPGA A supports the 3 ODI plus 8 10GbE IO operation.

There is one "B" configuration for FPGA B which is used for both startup options.

The following table outlines the FPGA resources which are available for custom logic within the sandbox per FPGA.

( Note these values are less than the total FPGA resources within the chip, due to the requirement to provide infrastructure within the FPGA to support the customer accessible area).

The two different configurations for FPGA A have the same amount of resources within the customer accessible area, FPGA B has slightly less available resource due to static area signal requirements for routing to the PCB.

| Resource Type           | Resource Size for customer region A | Resource Size for customer region B |

|-------------------------|-------------------------------------|-------------------------------------|

| CLB Flip-FLops (k)      | 1,584                               | 1,530                               |

| CLB LUTs (k)            | 792                                 | 765                                 |

| Max Dist. RAM (Mb)      | 24.8                                | 23.9                                |

| Total Block RAM (Mb)    | 50.625                              | 48.1                                |

| Ultra RAM (Mb)          | 229.5                               | 225                                 |

| Clock Mgmt Tiles (CMTs) | 62                                  | 60                                  |

| DSP Slices              | 4,848                               | 4224                                |

| Global Buffers          | 1020                                | 1032                                |

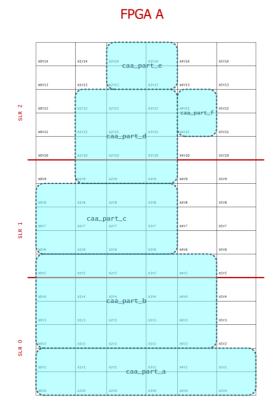

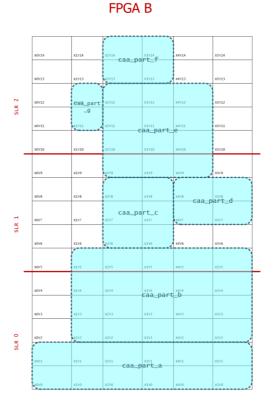

The figure below shows in pale blue shading the customer accessible areas for the two FPGA.

#### Available Configurations

There are two configurable regions per M8132A, one per FPGA.

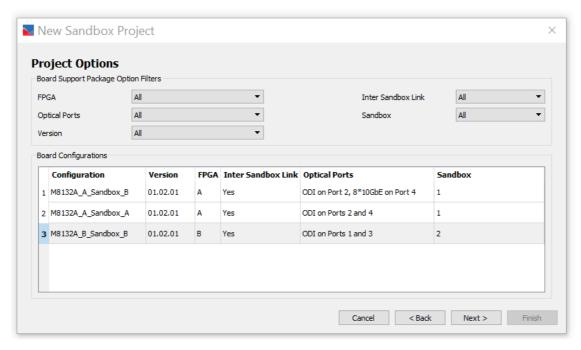

There is one supported FSP version, with two configurations for FPGA A, and one configuration for FPGA B, M8132A\_A\_Sandbox\_A, M8132A\_A\_Sandbox\_B and M8132A\_B\_Sandbox\_B.

The table below shows the mapping of the static region with the various configurations to allow the user to determine which configuration to use when creating partial designs.

| Connectivity          | Customer Accessible<br>Area A<br>configurations | Customer<br>Accessible<br>Area A<br>main ports | Customer Accessible<br>Area B<br>configurations | Customer<br>Accessible<br>Area B<br>main ports |

|-----------------------|-------------------------------------------------|------------------------------------------------|-------------------------------------------------|------------------------------------------------|

| 3 ODI plus<br>8 10GbE | M8132A_A_Sandbox_B                              | 1 ODI, 8<br>10GbE<br>Ethernet,<br>DPU2DPU      | M8132A_B_Sandbox_B                              | 2 ODI,<br>DPU2DPU                              |

| 4 ODI                 | M8132A_A_Sandbox_A                              | 2 ODI,<br>DPU2DPU                              | M8132A_B_Sandbox_B                              | 2 ODI,<br>DPU2DPU                              |

The figure below shows in an alternate view to the table above, the main differences between the two startup options.

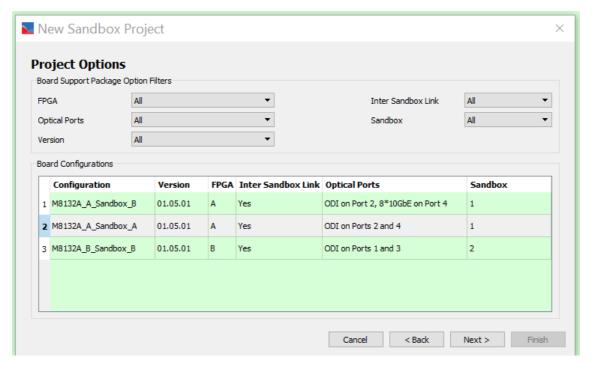

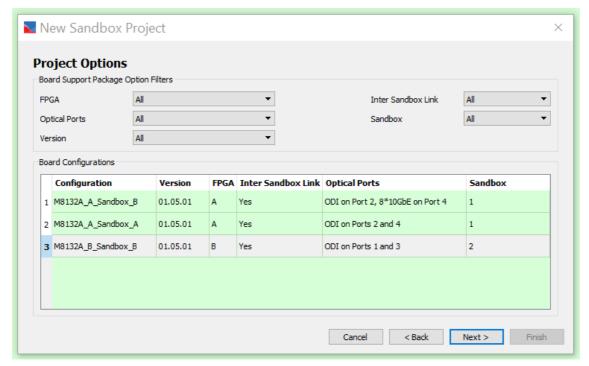

The screenshot below shows one stage of the New Sandbox Project dialog within the Pathwave FPGA tool, with the 3 different configurations available shown. Various filters can be applied to narrow down to the particular configuration to use depending on the optical interfaces desired in the design.

#### Port Mapping

The image above shows a CAD representation of the front panel of the M8132A module. The steel spring loaded shutters protect the optical interfaces. See the main M8132A User Guide for more details on the various input and output signals and connectors.

Of interest here is the mapping between the front panel ports and the two FPGA and the Customer Accessible Areas.

FPGA B is connected to the Optical ports 1 and 3, and these ports are always ODI.

FPGA A is connected to the Optical ports 2 and 4, with port 2 always carrying ODI, while port 4 will either have an ODI interface or eight 10GbE interfaces. See the M8132A User Guide for more details on the optical fibers required for connection to the module.

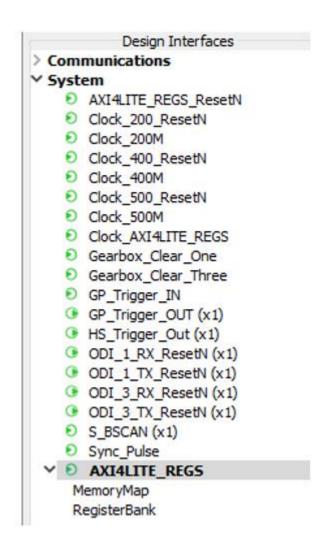

#### FPGA Configurable Region Interfaces

The following sections describe the physical interfaces which are available within a M8132A FPGA configurable region.

The ODI interfaces are synchronous to Clock\_ODI.

The AXI4Lite interface for register write and read is synchronous to Clock\_AXI4LITE\_REGS

The 10Gb Ethernet interfaces are synchronous to Clock\_400M

The DPU2DPU inter-CAA links are synchronous to Clock\_400M

The trigger signals are synchronous to Clock\_400M. Please see the module's User's Guide for a more detailed discussion of the trigger system before using these signals.

#### ODI - Optical Data Interface

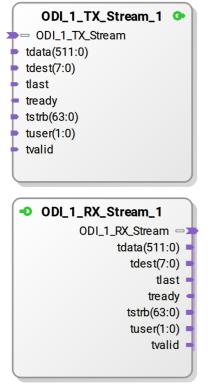

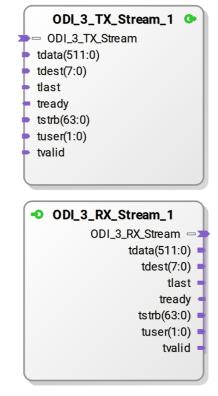

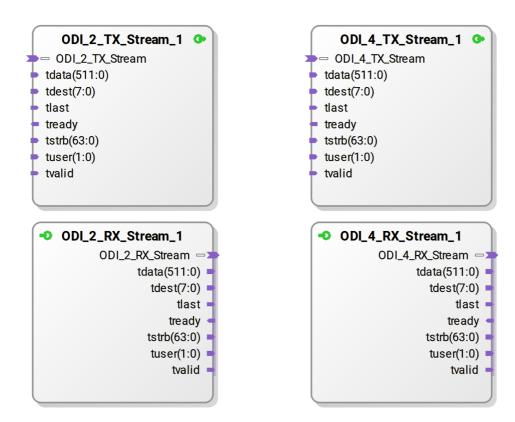

There are either one or two ODI interface per configurable region, each ODI interface is separated between transmit (TX) and receive (RX)

Customer Region B Sandbox 2 always has 2 ODI interfaces available, connected to Port 1 and Port 3

Customer Region A Sandbox 1 either has 1 ODI interface, connected to Port 2, or two ODI interfaces, connected to Port 2 and Port 4 available, depending on which configuration is used, to match the startup options of the M8132A Soft Front Panel.

The signals are synchronous with Clock\_ODI, (332MHz)

ODI\_2\_RX\_Stream and ODI\_4\_RX\_Stream are inputs to partial region 1, within FPGA A

ODI\_2\_TX\_Stream and ODI\_4\_TX\_Stream are outputs from partial region 1, within FPGA A

ODI\_1\_RX\_Stream and ODI\_3\_RX\_Stream are inputs to partial region 2, within FPGA B

ODI\_1\_TX\_Stream and ODI\_3\_TX\_Stream are outputs from partial region 1, within FPGA B

ODI\_4\_TX\_Stream and ODI\_4\_RX\_Stream are only available within the configuration M8132A\_A\_Sandbox\_A, the configuration for use with a 4 ODI startup.

| Interface Name and Type    | Signal<br>Name | Width (bits) | Bit<br>Field | Description                                                                                                                                                                                                                                                                                          |

|----------------------------|----------------|--------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ODI_X_TX_Stream<br>: AXI4S |                |              |              | AXI4 Streaming interface for connection to the transmit half of an ODI port with a 512Bit data interface, and various sideband channels. Data format is variable, but includes RAW ODI, or Vita-49 wrapped ODI depending on the local source generating the data within the customer accessible area |

|                            | tvalid         | 1            |              | input to interface, standard AXI4S use                                                                                                                                                                                                                                                               |

|                            | tready         | 1            |              | output from interface, standard AXI4S use                                                                                                                                                                                                                                                            |

|                            | tdata          | 512          |              | input to interface, 512bit, 64 byte data, must<br>be qualified by the TSTRB signal. Either the<br>full 64 bytes, or the upper 32 bytes are only<br>valid combinations of data. ODI Packet Data<br>can be either odd or even multiple of 32bytes<br>long. Minimum size is 64bytes                     |

| tdest                      | tdest          | 8            |              | input to interface, maps to the ODI channel number                                                                                                                                                                                                                                                   |

|                            | tlast          | 1            |              | input to interface, indicates this current transfer includes the last transfer of a packet                                                                                                                                                                                                           |

| Interface Name and Type    | Signal<br>Name | Width (bits) | Bit<br>Field | Description                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------|----------------|--------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | tstrb          | 64           |              | input to interface, qualifies the data, only two values are valid, either 0xFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF                                                                                                                                                                                                                                                                               |

|                            | tuser          | 2            | 1            | Input to interface, err_in, allows the user to indicate something is wrong with the current packet being sent into the interface, only valid when TLAST is true. This indicator will be passed out at the far end allowing the receiving device to take action if appropriate.                                                                                                                 |

|                            |                |              | 0            | Input to interface, "midword" indicator. Only valid when TLAST is true.  If the current transfer is a full 64byte transfer, and TLAST is true, midword as 0 indicates the bottom 32 bytes is the last portion of the current packet. If midword is a 1, this indicates that the top 32bytes is the last portion of one packet, and the bottom 32bytes is the first portion of the next packet. |

| ODI_X_RX_Stream<br>: AXI4S |                |              |              | AXI4 Streaming interface for connection to<br>the receive half of an ODI port with a 512Bit<br>data interface, and various sideband<br>channels. Data format is variable, but<br>includes RAW ODI, or Vita-49 wrapped ODI<br>depending on the remote source generating<br>the data                                                                                                             |

|                            | tvalid         | 1            |              | output from interface, standard AXI4S use                                                                                                                                                                                                                                                                                                                                                      |

|                            | tready         | 1            |              | input to interface, standard AXI4S use                                                                                                                                                                                                                                                                                                                                                         |

|                            | tdata          | 512          |              | output from interface, 512bit, 64 byte data, is qualified by the TSTRB signal. Either the full 64 bytes, or the upper 32 bytes are valid combinations of data. ODI Packet Data can be either odd or even multiple of 32bytes long. Minimum size is 64bytes                                                                                                                                     |

|                            | tdest          | 8            |              | output from interface, maps to the ODI channel number                                                                                                                                                                                                                                                                                                                                          |

|                            | tlast          | 1            |              | output from interface, indicates this current transfer includes the last transfer of a packet                                                                                                                                                                                                                                                                                                  |

|                            | tstrb          | 64           |              | ouput from interface, qualifies the data, only two values are valid, either OxFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF                                                                                                                                                                                                                                                                             |

|                            | tuser          | 2            | 1            | output from interface, err_out, allows the user to be informed that something is wrong with the current packet being received from the interface, only valid when TLAST is true. This indicator may have been passed in at the far end before transmission, or it was generated by the ODI cores to indicate a transmission                                                                    |

| Interface Name and Type | Signal<br>Name | Width (bits) | Bit<br>Field | Description                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------|----------------|--------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |                |              |              | error of some sort, allowing the receiving device to take action if appropriate.                                                                                                                                                                                                                                                                                                                 |

|                         |                |              | 0            | output from interface, "midword" indicator. Only valid when TLAST is true. If the current transfer is a full 64byte transfer, and TLAST is true, midword as 0 indicates the bottom 32 bytes is the last portion of the current packet. If midword is a 1, this indicates that the top 32bytes is the last portion of one packet, and the bottom 32bytes is the first portion of the next packet. |

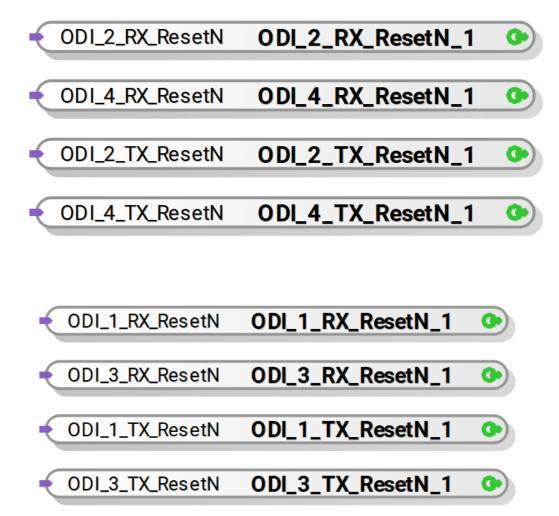

#### **ODI Resets**

Each ODI port has a separate reset that should be driven by user logic

This reset acts upon the AXI4S interface of the ODI function within the static area, it does not reset the optical side of the ODI function

The reset should be driven and released before users try to transmit to or receive from an ODI port.

In general, In the case of receiving from an ODI port, the local RX Interface should be reset and the user logic waiting to receive before the far end remote device starts transmitting.

If receive flow control is active on the local ODI interface in the static region, and the far end remote device supports flow control, then once the local RX interface reset is released, the far end remote device could start transmission, before the local logic is ready, with the flow control holding off the far end until the local logic starts receiving

| Interface Name  | signal<br>name | Width (bits) | Bit<br>Field | Description                                                      |

|-----------------|----------------|--------------|--------------|------------------------------------------------------------------|

| ODI_X_TX_ResetN |                | 1            |              | input to interface, resets the user side of the tx ODI Interface |

| Interface Name  | signal<br>name | Width (bits) | Bit<br>Field | Description                                                      |

|-----------------|----------------|--------------|--------------|------------------------------------------------------------------|

| ODI_X_RX_ResetN |                | 1            |              | input to interface, resets the user side of the rx ODI Interface |

#### ODI Startup reset

There is no individual ODI startup reset, if one is needed, use a suitable synchronization method to create one from the 400M startup reset signal "Clock\_400\_ResetN"

#### **ODI Receive Status**

These three signals provide a means for the user logic within the configurable region to monitor the status of the flow control fifo within the static area ODI function.

| Interface name      | Signal name | Width (bits) | Bit<br>Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------|-------------|--------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| odi_X_rx_prog_full  |             | 1            |              | output from interface, the ODI interface in the static area has a programmable depth guide for the internal fifo, this bit represents the current depth as being above if true, or below, if false, the current set level                                                                                                                                                                                                           |

| odi_X_rx_fifo_depth |             | 10           |              | output from interface, the ODI interface in the static area has a fifo for dealing with flow control, this output represents the current depth                                                                                                                                                                                                                                                                                      |

| odi_X_rx_ovf        |             | 1            |              | output from interface, the ODI interface in the static area has a fifo for dealing with flow control, this output represents the fact that the far end ignored local flow control messages send to the far end, and caused the fifo to fill, and have more information arrive that was dropped and not written to the fifo. This is an error condition, the ODI interface needs deactivated and reactivated to clear this condition |

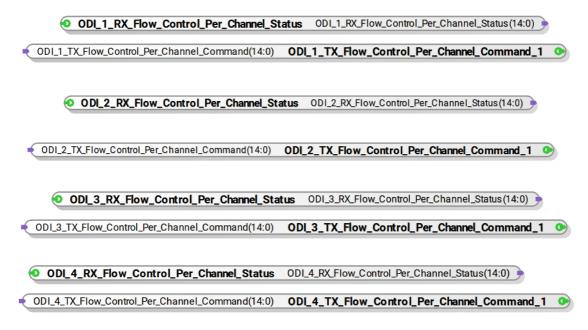

#### ODI Per Channel Flow Control

For Future Use

ODI Clock

| Interface Name and Type | Signal<br>Name | Width (bits) | Description                                                                          |

|-------------------------|----------------|--------------|--------------------------------------------------------------------------------------|

| Clock_ODI               |                | 1            | ODI interface clock, 332MHz The ODI AXI4S interfaces are synchronous with this clock |

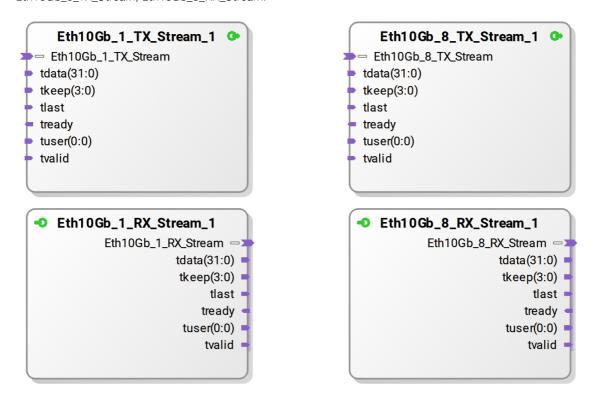

#### 10Gbe Ethernet Interface

Configuration M8132A\_A\_Sandbox\_B gives the user the choice to connect up to to eight 10Gb Ethernet interfaces instead of the ODI interface on optical port 4

Each Ethernet interface is separated between transmit (TX) and receive (RX)

The picture here just shows the first pair, Eth10Gb\_1\_TX\_Stream, Eth10Gb\_1\_RX, and the last pair, Eth10Gb\_8\_TX\_Stream, Eth10Gb\_8\_RX\_Stream.

The other 10GbE Ethernet Interfaces, 2 to 7 have the same connectivity.

The signals are synchronous with Clock\_400M, (400MHz) They are transferred to/from 312.5Mhz clocks in the static area.

Eth10Gb\_1\_RX\_Stream to Eth10Gb\_8\_RX\_Stream are inputs to partial region 1, within FPGA A of configuration M8132A\_A\_Sandbox\_B

$\label{th:configuration} Eth 10 Gb\_1\_TX\_Stream\ to\ Eth 10 Gb\_8\_TX\_Stream\ are\ outputs\ from\ partial\ region\ 1,\ within\ FPGA\ A\ of\ configuration\ M8132A\_A\_Sandbox\_B$

| Interface Name and Type        | Signal<br>Name | Width (bits) | Bit<br>Field | Description                                                                                                                                                    |

|--------------------------------|----------------|--------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Eth10Gb_X_TX_Stream<br>: AXI4S |                |              |              | AXI4 Streaming interface for connection to the transmit half of an Ethernet port with a 32Bit data interface, and various sideband channels.                   |

|                                | tvalid         | 1            |              | input to interface, standard AXI4S use                                                                                                                         |

|                                | tready         | 1            |              | output from interface, standard AXI4S use                                                                                                                      |

|                                | tdata          | 32           |              | input to interface, 32bit, 4 byte data. When tlast is low all 4 bytes are valid. When tlast is high 1-4 bytes will be valid according to the settings on tkeep |

| Interface Name and Type        | Signal<br>Name | Width (bits) | Bit<br>Field | Description                                                                                                                                                                                                                                                                                                                 |

|--------------------------------|----------------|--------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                | tlast          | 1            |              | input to interface, indicates this current<br>transfer includes the last transfer of a<br>packet                                                                                                                                                                                                                            |

|                                | tkeep          | 4            |              | input to interface, qualifies the last word of data, "1111"2 indicates all 4 bytes (bits 31:0) are valid. "0111"2 indicates 3 bytes (bits 23:0) are valid. "0011"2 indicates 2 bytes (bits 15:0) are valid. "0001"2 indicates 1 byte is valid. All other patterns on tkeep are invalid. Only relevant when tlast is set.    |

|                                | tuser          | 1            |              | Input to interface, should be set if the customer cannot finish the current packet.                                                                                                                                                                                                                                         |

| Eth10Gb_X_RX_Stream<br>: AXI4S |                |              |              | AXI4 Streaming interface for connection to the receive half of an Ethernet port with a 32Bit data interface, and various sideband channels.                                                                                                                                                                                 |

|                                | tvalid         | 1            |              | output from interface, standard AXI4S use                                                                                                                                                                                                                                                                                   |

|                                | tready         | 1            |              | input to interface, standard AXI4S use                                                                                                                                                                                                                                                                                      |

|                                | tdata          | 32           |              | output from interface, 32bit, 4 byte data. When tlast is low all 4 bytes are valid. When tlast is high 1-4 bytes will be valid according to the settings on tkeep.                                                                                                                                                          |

|                                | tlast          | 1            |              | output from interface, indicates this current transfer includes the last transfer of a packet                                                                                                                                                                                                                               |

|                                | tkeep          | 4            |              | output from interface, qualifies the last word of data, "1111"2 indicates all 4 bytes (bits 31:0) are valid. "0111"2 indicates 3 bytes (bits 23:0) are valid. "0011"2 indicates 2 bytes (bits 15:0) are valid. "0001"2 indicates 1 byte is valid. All other patterns on tkeep are invalid. Only relevant when tlast is set. |

|                                | tuser          | 1            | 0            | output from interface. valid at the same time as tlast. Indicates something wrong with the packet.  Error conditions include packet too short, packet too long, FCS error, XGMII code error or bad control frame received.                                                                                                  |

When a packet is transmitted over the interface there should be no gaps in tvalid for the duration of the packet. In the receive direction rx tready should be high always. The receiver is not allowed to push back.

#### 10Gbe Ethernet Resets

| <b>(2)</b> | Eth10Gb_3_TX_ResetN | Eth10Gb_3_TX_ResetN |  |

|------------|---------------------|---------------------|--|

|            |                     |                     |  |

Eth10Gb\_3\_RX\_ResetN Eth10Gb\_3\_RX\_ResetN >

Eth10Gb\_5\_TX\_ResetN Eth10Gb\_5\_TX\_ResetN >

Eth10Gb\_5\_RX\_ResetN Eth10Gb\_5\_RX\_ResetN

Each Ethernet port has a separate reset input that should be connected to user logic

The diagram above only illustrates the resets for the transmit and receive ports for Ethernet channels 3 and 5, there are transmit and receive resets for all 8 Ethernet transmit and receive channels.

These resets come from the 10Gb Ethernet functionality in the static area, and should be used to reset user logic within the Customer Accessible Area

| Interface Name      | signal<br>name | Width (bits) | Bit<br>Field | Description                                                                                   |

|---------------------|----------------|--------------|--------------|-----------------------------------------------------------------------------------------------|

| Eth10Gb_X_TX_ResetN |                | 1            |              | output from the interface, should be used to reset the user logic transmit Ethernet circuitry |

| Interface Name      | signal<br>name | Width (bits) | Bit<br>Field | Description                                                                                  |

|---------------------|----------------|--------------|--------------|----------------------------------------------------------------------------------------------|

| Eth10Gb_X_RX_ResetN |                | 1            |              | output from the interface, should be used to reset the user logic receive Ethernet circuitry |

#### 10GbE Ethernet Receive Status

| <b>(2)</b> | Eth10Gb_2_RX_Status | Eth10Gb_2_RX_Status(2:0) |

|------------|---------------------|--------------------------|

|            |                     |                          |

Eth10Gb\_7\_RX\_Status Eth10Gb\_7\_RX\_Status(2:0)

Each Ethernet receive port has a low speed status feed, the signals are synchronous with the 400MHz clock Clock\_400M, but are not related to any particular AXI4S transaction on the main Ethernet Channel's streams.

| Interface Name and Type        | Signal<br>Name | Width (bits) | Bit<br>Field | Description                                                                                                                                                                                                                             |   |                                                                                                                                                                    |

|--------------------------------|----------------|--------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Eth10Gb_X_RX_Status: 3 bit Bus |                | 3            | 2            | Block Lock Status: this indicates teh<br>Ethernet MAC within the static area for<br>this channel is assering that the<br>receiver has achieved block lock as<br>defined in Clause 49.2.14 of IEEE<br>802.3, level senstive, active high |   |                                                                                                                                                                    |

|                                |                |              |              |                                                                                                                                                                                                                                         | 1 | Remote Fault Alarm: this indicates the Ethernet MAC within the static area for this channel is asserting the remote fault larm signal, level sensitve, active high |

|                                |                |              | 0            | Local Fault Alarm: this indicates the Ethernet MAC within the static area for this channel is asserting the local fault alarm signal, level sensitive, active high                                                                      |   |                                                                                                                                                                    |

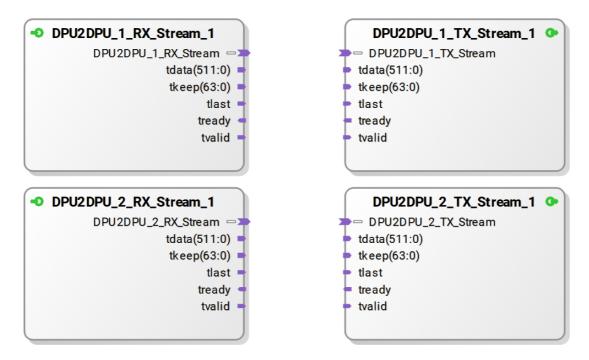

#### DPU2DPU

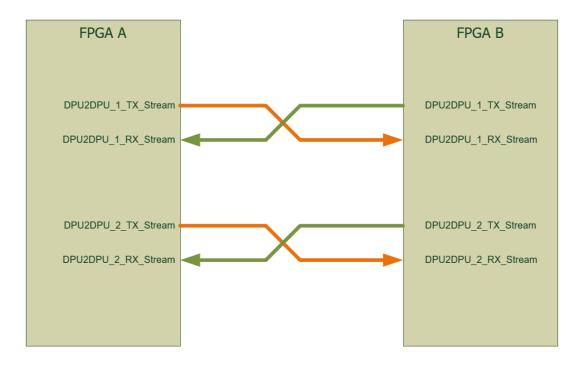

There are two DPU2DPU AXI4S interfaces which permit transfer of data between the two Customer Accessible Areas, i.e. between Sandbox 1 and Sandbox 2

The two links are bidirectional, and are provided as separate transmit and receive streams

The signals are synchronous with the Clock\_400M

| Interface Name and Tyres       | Cianal         | Width  | Dit          | Description                                                                                                                                                        |

|--------------------------------|----------------|--------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interface Name and Type        | Signal<br>Name | (bits) | Bit<br>Field | Description                                                                                                                                                        |

| DPU2DPU_X_TX_Stream<br>: AXI4S |                |        |              | AXI4 Streaming interface for connection to the transmit half of a DPU2DPU port with a 512Bit data interface, and various sideband channels.                        |

|                                | tvalid         | 1      |              | input to interface, standard AXI4S use                                                                                                                             |

|                                | tready         | 1      |              | output from interface, standard AXI4S use                                                                                                                          |

|                                | tdata          | 512    |              | input to interface, 512bit, 64 byte data. When tlast is low all 64 bytes are valid. When tlast is high 1-64 bytes will be valid according to the settings on tkeep |

|                                | tlast          | 1      |              | input to interface, indicates this current transfer includes the last transfer of a packet                                                                         |

|                                | tkeep          | 64     |              | input to interface, qualifies the last word of data, "ffffffffffffffffffffffffffffffffffff                                                                         |

| Interface Name and Type        | Signal<br>Name | Width (bits) | Bit<br>Field | Description                                                                                                                                                            |

|--------------------------------|----------------|--------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DPU2DPU_X_RX_Stream<br>: AXI4S |                |              |              | AXI4 Streaming interface for connection to the receive half of a DPu2DPU port with a 32Bit data interface, and various sideband channels.                              |

|                                | tvalid         | 1            |              | output from interface, standard AXI4S use                                                                                                                              |

|                                | tready         | 1            |              | input to interface, standard AXI4S use                                                                                                                                 |

|                                | tdata          | 512          |              | output from interface, 512bit, 64 byte data. When tlast is low all 64 bytes are valid. When tlast is high 1-64 bytes will be valid according to the settings on tkeep. |

|                                | tlast          | 1            |              | output from interface, indicates this current transfer includes the last transfer of a packet                                                                          |

|                                | tkeep          | 64           |              | ouput from interface, qualifies the last word of data, "ffffffffffffffffffffffffffffffffffff                                                                           |

Data sent to one of the TX interface of Sandbox 1 will appear at the appropriate RX interface of Sandbox 2. Similarly, data sent to one of the TX interface of Sandbox 2 will appear at the appropriate RX interface of Sandbox 1.

The Receiver side should be started, and assert tready on the "listening" sandbox before the transmission on the "speaking" sandbox side is started. There are fifos within the static area to handle clock domain crossing, but they are not large enough to handle very much data before they fill and data is dropped, there is no back-pressure on the actual inter chip links, so data will be dropped if the transmitter is started before the receiver is ready.

There is back pressure on the transmit clock domain crossing fifo in the sending side interface of the static area, so user code within the CA must obey the usual AXI4S tready signal on that interface to prevent data loss

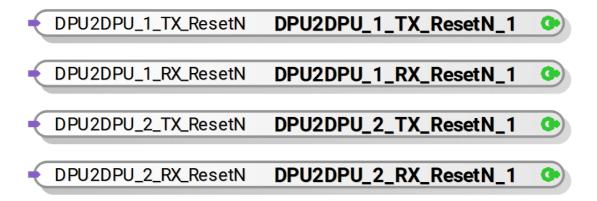

#### **DPU2DPU Resets**

Each DPU2DPU port has a separate reset that should be driven by user logic

This reset acts upon the AXI4S interface of the DPU2DPU function within the static area, it does not reset the actual links between the FPGA

The reset should be driven and released before users try to transmit to or receive from a DPU2DPU port.

| Interface Name      | signal<br>name | Width (bits) | Bit<br>Field | Description                                                                                                 |

|---------------------|----------------|--------------|--------------|-------------------------------------------------------------------------------------------------------------|

| DPU2DPU_X_TX_ResetN |                | 1            |              | input to interface, resets the user side of the tx DPU2DPU interface logic in the static region of the FPGA |

| Interface Name      | signal<br>name | Width (bits) | Bit<br>Field | Description                                                                                                 |

|---------------------|----------------|--------------|--------------|-------------------------------------------------------------------------------------------------------------|

| DPU2DPU_X_RX_ResetN |                | 1            |              | input to interface, resets the user side of the rx DPU2DPU interface logic in the static region of the FPGA |

#### **DPU2DPU Receive Status**

DPU2DPU\_1\_RX\_Monitor\_Overflow

DPU2DPU\_1\_RX\_Monitor\_Overflow

DPU2DPU\_1\_RX\_Monitor\_Fifo\_Depth

DPU2DPU\_2\_RX\_Monitor\_Overflow

DPU2DPU\_2\_RX\_Monitor\_Overflow

DPU2DPU\_2\_RX\_Monitor\_Fifo\_Depth

DPU2DPU\_2\_RX\_Monitor\_Fifo\_Depth

These two signals provide a means for the user logic within the configurable region to monitor the status of the dpu2dpu link within the static region of the FPGA

| Interface name                  | Signal name | Width (bits) | Bit<br>Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------|-------------|--------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DPU2DPU_X_RX_Monitor_Overflow   |             | 1            |              | output from interface, if the far end transmits before the receiver is ready, the clock domain crossing fifo in the static area can overflow, which this bit records, cleared with the appropriate DPU2DPU_X_RX_ResetN signal                                                                                                                                                                                                                                                                                                                 |

| DPU2DPU_X_RX_Monitor_Fifo_Depth |             | 8            |              | output from interface, the DPU2DPU interface in the static area has a fifo for handling clock domain crossing. There is no push back from the local receiver to the far end transmitter, this signal allows a user to monitor how deep the fifo is being filled. Note there will be some delay in this interface updating as data arrives in this FPGA's static region over the DPU2DPU link from the far end. Any receiver logic in this sandbox should be capable of receiving whatever the transmitter in the other FPGA sandbox transmits |

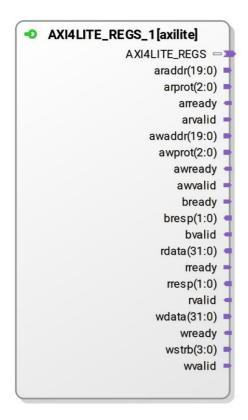

#### Register Access

There is one Register access port per configurable region, the signals are synchronous with  $clock\_AXI4LITE\_REGS$ , which runs at 125MHz

The user can choose between adding "RegisterBank" components, which hide the AXI4Lite bus, and use prebuilt register components, or can have the full AXI4Lite bus for connecting to their own register system

| Interface Name and Type     | Signal<br>Name | Width (bits) | Bit<br>Field | Description                                                                                                                                                                          |

|-----------------------------|----------------|--------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register :<br>AXI4LITE_REGS |                |              |              | Register access interface, Up to 1Mbyte space, accessed in 4byte/32bit registers, i.e. 252,144 maximum registers ( subject to place and route constraints, resource limitations etc) |

|                             | awprot         | 3            | 2:0          | output from interface, normal axi4Lite operation                                                                                                                                     |

|                             | awvalid        | 1            |              | output from interface, normal axi4Lite operation                                                                                                                                     |

|                             | awready        | 1            |              | intput to interface, normal axi4Lite operation                                                                                                                                       |

|                             | awaddr         | 20           | 19:0         | output from interface, normal axi4Lite operation                                                                                                                                     |

|                             | bready         | 1            |              | output from interface, normal axi4Lite operation                                                                                                                                     |

|                             | bvalid         | 1            |              | input to interface, normal axi4Lite operation                                                                                                                                        |

|                             | bresp          | 2            | 1:0          | input to interface, normal axi4Lite operation                                                                                                                                        |

| Interface Name and Type | Signal<br>Name | Width (bits) | Bit<br>Field | Description                                          |

|-------------------------|----------------|--------------|--------------|------------------------------------------------------|

|                         | wvalid         | 1            |              | output from the interface, normal axi4Lite operation |

|                         | wready         | 1            |              | input to the interface, normal axi4Lite operation    |

|                         | wdata          | 32           | 31:0         | output from the interface, normal axi4Lite operation |

|                         | arprot         | 3            | 2:0          | output from interface, normal axi4Lite operation     |

|                         | arvalid        | 1            |              | output from the interface, normal axi4Lite operation |

|                         | arready        | 1            |              | input to the interface, normal axi4Lite operation    |

|                         | araddr         | 20           | 19:0         | output from the interface, normal axi4Lite operation |

|                         | rvalid         | 1            |              | intpuit to the interface, normal axi4Lite operation  |

|                         | rready         | 1            |              | output from the interface, normal axi4Lite operation |

|                         | rresp          | 2            | 1:0          | input to the intrface, normal axi4Lite operation     |

|                         | rdata          | 32           | 31:0         | input to the interface, normal axi4Lite operation    |

## Register Reset

| Interface Name and Type | Signal<br>Name | Width (bits) | Bit<br>Field | Description                                            |

|-------------------------|----------------|--------------|--------------|--------------------------------------------------------|

| AXI4LITE_REGS_ResetN    |                | 1            |              | output from the interface, resets all slave interfaces |

## Register Clock

| Interface Name and Type | Signal<br>Name | Width (bits) | Description                                                                                                       |

|-------------------------|----------------|--------------|-------------------------------------------------------------------------------------------------------------------|

| Clock_AXI4LITE_REGS     |                | 1            | Register access interface clock, 125MHz The AXI4Lite interface for register access is synchronous with this clock |

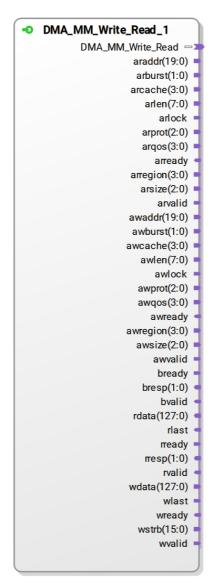

#### Memory Mapped DMA Access

For Future Use

Memory Mapped DMA Reset

For Future Use

Memory Mapped DMA Clock

For Future Use

Clock 400M

| Interface<br>Name and<br>Type | Signal<br>Name | Width (bits) | Description                                                                                                                                                                                                                                                                                                                                |

|-------------------------------|----------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock_400M                    |                | 1            | Main data processing clock for 400bit, 40 samples at 10bits per sample For deterministic latency between an M8131A and an M8132A, this clock and a 40 times super sample 10bit scheme must be employed, further the reference input of the M8132A must be connected to the reference output of the M8132A to lock the 400M clocks together |

400M Reset

# Clock\_400\_ResetN Clock\_400\_ResetN >

| Interface Name and Type | Signal<br>Name | Width (bits) | Description                                                                                                            |

|-------------------------|----------------|--------------|------------------------------------------------------------------------------------------------------------------------|

| Clock_400_ResetN        |                |              | Startup reset, synchronous to 400M clock, active low, Set active at programming, goes inactive "TBD" 400M clocks later |

Clock 500M

| Interface<br>Name and<br>Type | Signal<br>Name | Width (bits) | Description                                                                                                                                                                                                                                                                                                |

|-------------------------------|----------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock_500M                    |                | 1            | Main data processing clock for 320bit, 32 samples at 10bits per sample Some tools for creating FPGA processing RTL automatically work better with power of two super sampling. This clock in conjunction with fifos and gearboxes can be used to convert a 400bit@400M data path to a 320bit@500M datapath |

500M Reset

| Interface Name and Type | Signal<br>Name | Width (bits) | Description                                                                                                            |

|-------------------------|----------------|--------------|------------------------------------------------------------------------------------------------------------------------|

| Clock_500M_ResetN       |                | 1            | Startup reset, synchronous to 500M clock, active low, Set active at programming, goes inactive "TBD" 500M clocks later |

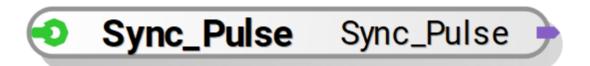

Sync Puse

See the M132A user guide for details on how to employ the sync pulse mechanism

| Interface Name and Type | Signal<br>Name | Width (bits) | Description                                                                                  |

|-------------------------|----------------|--------------|----------------------------------------------------------------------------------------------|

| Sync_Pulse              |                | 1            | Signal for co-ordination of operations across multiple FPGA, synchronous with the 400M clock |

GP\_Trigger\_IN

# GP\_Trigger\_IN GP\_Trigger\_IN(2:0)

Functionality is controlled by software which controls the mapping of various input signals of the module front panel to the connections of the Sandbox, see the M8132A user guide for more details

| Interface Name and Type | Signal Name   | Width (bits) | Bit<br>Field | Description                                                                       |

|-------------------------|---------------|--------------|--------------|-----------------------------------------------------------------------------------|

| GP_Trigger_IN           |               |              |              | General Purpose triggers into<br>the Sandbox,<br>synchronous to the 400M<br>clock |

|                         | GP_Trigger_IN | 3            | 2:0          | input to the sandbox                                                              |

GP\_Trigger\_OUT

## GP\_Trigger\_OUT(2:0) GP\_Trigger\_OUT\_1 •

Functionality is controlled by software which controls the mapping of the connections of the Sandbox to various output signals of the module front panel, see the M8132A user guide for more details

| Interface Name and Type | Signal Name    | Width (bits) | Bit<br>Field | Description                                                                           |

|-------------------------|----------------|--------------|--------------|---------------------------------------------------------------------------------------|

| GP_Trigger_OUT          |                |              |              | General Purpose triggers out<br>from the Sandbox,<br>synchronous to the 400M<br>clock |

|                         | GP_Trigger_OUT | 3            | 2:0          | output from the sandbox                                                               |

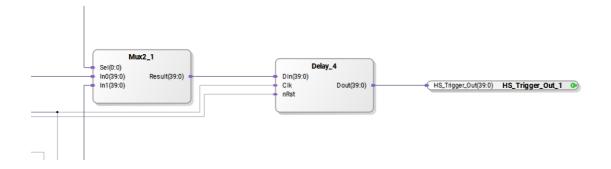

# HS\_Trigger\_Out(39:0) HS\_Trigger\_Out\_1 •

The High Speed Trigger out connects to the SMA output on the front panel of the M8132A

| Interface Name and Type | Signal Name    | Width (bits) | Bit<br>Field | Description                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------|----------------|--------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HS_Trigger_Out          |                |              |              | Source of signal to feed to the Front panel SMA connector synchronous to the 400M clock                                                                                                                                                                                                                                                                     |

|                         | HS_Trigger_Out | 40           | 39:0         | output from the sandbox For instance, it could be used to feed the MSB of each of the 40 samples of the 400 bit 10 times super-sample bus at 400M within the sandbox when working with 10bit data, to create a waveform on the trigger out SMA, synchronous to the received data over ODI after it has been passed through an appropriate fifo and gearbox. |

Gearbox Clear

- Gearbox\_Clear\_Three Gearbox\_Clear\_Three

- Gearbox\_Clear\_Two Gearbox\_Clear\_Two

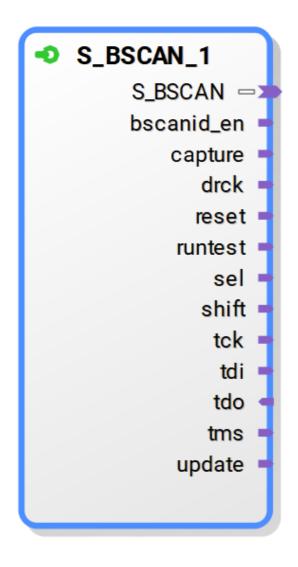

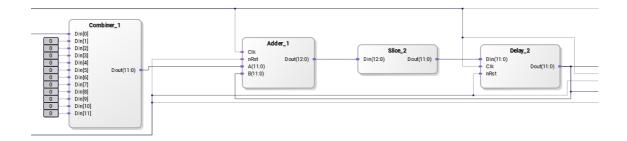

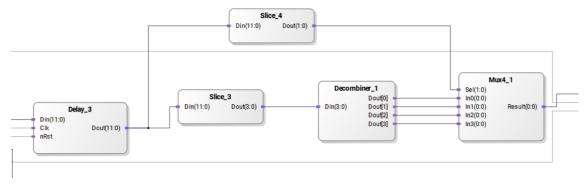

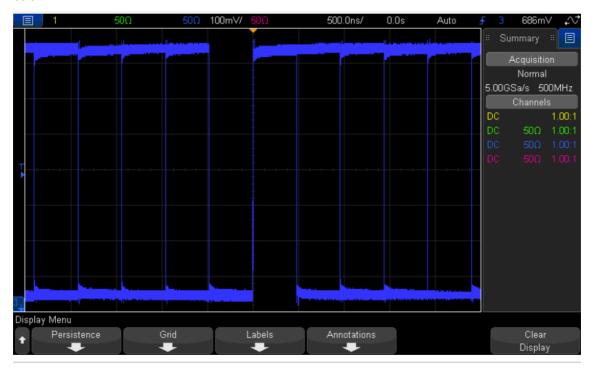

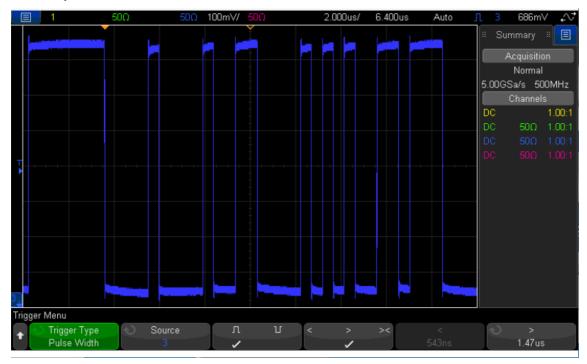

- Gearbox\_Clear\_Four Gearbox\_Clear\_Four