| DDR5 is Coming, Are You Ready?

Accurate Statistical-Based DDR Margin Estimation

JEDEC plans to release the new DDR5 standard in 2018. DDR5 will provide double the bandwidth and density over DDR4, pushing the speed grade from 3.2 to 6.4 Gbps. Without a doubt, Rx equalization will be necessary to handle the closed eye in the DDR5 system. Random and deterministic jitter will play a more important role as well. This presentation will introduce a breakthrough simulation technology designed to help you with your DDR5 and DDR4 design challenges. You will learn how to predict the noise and jitter distribution at ultra-low BER and account for Rx equalization in the parallel bus simulation. > Slides (PDF, 3.31 MB) > Technical Seminar Video |

| Demystifying VIAs in High-Speed PCB Design

A high-speed signal traveling vertically through the board layer is several times more complex and difficult to analyze than a signal traveling horizontally along the same layer. This presentation covers the basics of VIA construction and its impact to high-speed signals. We will also highlight tips for better VIA design and introduce different simulation techniques for generating more transparent interconnects and allow you to make various tradeoffs. > Slides (PDF, 3.58 MB) > Technical Seminar Video |

| How Much Bandwidth Do I Need for My Channel Model?

Are You Killing Your Schedule and Increasing Uncertainty with Unnecessary 100GHz Full 3D EM Simulations?

How much bandwidth do you need for your channel model? The traditional answer has often been “As wide and as accurate as I can get!” to give you as much margin as possible against unknowns. However, this approach comes with the penalty of increased time and cost associated with simulation and equipment. Even then, you still don’t really know if what you have is good enough. How many system variables could you explore when each channel model run takes several days? The good news is that there are some simple approaches you can use to help you find that sweet spot between time, accuracy and cost using both frequency and time domain simulation techniques, so you can be confident about your model! > Slides (PDF, 14.7 MB) > Technical Seminar Video > Workspace (Knowledge Center login required) |

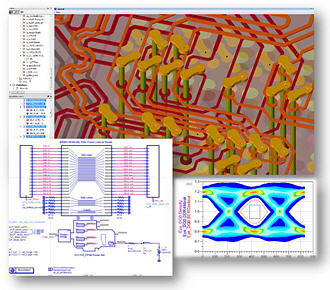

| Chronicles of a High-Speed PCB

Take a journey through a high speed PC board. We will start where the Layout engineer finishes. We will import the completed board into our board extraction tool, explore traces, select traces and extract their model. We will then take the extracted model in to our circuit simulation tool and run post layout circuit simulation to be able to better predict the system’s behavior. We will do this for a Serial channel, and a parallel channel as each design has its own challenges. By the end of this journey we can send the board to the fab house with confidence! > Slides (PDF, 5.72 MB) > Technical Seminar Video Chronicles of a High-Speed PCB including PCB Thermal Effects - Presented in Canada >Slides (PDF, 6.80 MB) |

| Power Integrity is More Than Decoupling Capacitors

Understanding The Power Integrity Ecosystem

Power Integrity is more than loop inductances and decoupling capacitors. Along with the power plane target impedances, the Power Integrity engineer also needs to consider the VRM model, and have some level of power electronics knowledge and understanding of how to bring all of these pieces together. This presentation details a Power Integrity ecosystem that covers all of these topics in an effort to help you design a better board. > Slides (PDF, 5.62 MB) > Technical Seminar Video > Videos ("How to Design for Power Integrity" YouTube video series) |

| PCI Gen-4: How Far Can a Bit Travel Before it Needs to Refuel?

End-to-End System-Level Simulation with Repeaters for PCIe Gen4

The design solution space is becoming increasingly complex for the PCIe Gen-4 system, especially when a repeater is needed to extend the reach between a Root Complex (RC) and End Point (EP) device. Since the repeater’s settings must be co-optimized with those of the Transmitter (Tx) and Receiver (Rx) to maximize overall link performance, the parameter tuning of active components becomes a daunting problem to tackle. This presentation details a “how-to” guide for defining, executing, and analyzing system-level simulations involving all three components. > Slides (PDF, 2.63 MB) > Technical Seminar Video |

At every turn, a newer, faster, better interconnect standard is proposed. Standard Working Groups are hard at work on next-generation protocols, trying to squeeze out more speed in the face of ever increasing constraints. When it comes to digital standards, every generational change introduces new challenges and risks, in particular, issues with Signal Integrity (SI) and Power Integrity (PI). Design success demands that today’s engineer have the skills needed to overcome these challenges and face down any risks. In this seminar, Keysight experts will share their industry expertise and present design, analysis and simulation solutions for effectively addressing signal integrity and power integrity challenges.

At every turn, a newer, faster, better interconnect standard is proposed. Standard Working Groups are hard at work on next-generation protocols, trying to squeeze out more speed in the face of ever increasing constraints. When it comes to digital standards, every generational change introduces new challenges and risks, in particular, issues with Signal Integrity (SI) and Power Integrity (PI). Design success demands that today’s engineer have the skills needed to overcome these challenges and face down any risks. In this seminar, Keysight experts will share their industry expertise and present design, analysis and simulation solutions for effectively addressing signal integrity and power integrity challenges.