# M8000 Series of BER Test Solutions

M8020A High-Performance BERT

M8040A High-Performance BERT 64 GBd

M8050A High-Performance BERT 120 GBd

# **Notices**

#### © Keysight Technologies 2024

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies as governed by United States and international copyright laws.

#### **Trademarks**

PCI Express® and PCIe® are registered trademarks of PCI-SIG.

# Manual Part Number M8000-91B08

#### Edition

Edition 14.0, April 2024 Keysight Technologies Deutschland GmbH Herrenberger Strasse 130, 71034 Böblingen, Germany

# **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

# U.S. Government Rights

The Software is "commercial computer software," as defined by Federal Acquisition Regulation ("FAR") 2.101. Pursuant to FAR 12.212 and 27.405-3 and Department of Defense FAR Supplement

("DFARS") 227.7202, the U.S. government acquires commercial computer software under the same terms by which the software is customarily provided to the public. Accordingly, Keysight provides the Software to U.S. government customers under its standard commercial license, which is embodied in its End User License Agree-

ment (EULA), a copy of which can be found at http://www.keysight.com/find/sweula.

The license set forth in the EULA represents the exclusive authority by which the U.S. government may use, modify, distribute, or disclose the Software. The EULA and the license set forth therein, does not require or permit, among other things, that Keysight: (1) Furnish technical information related to commercial computer software or commercial computer software documentation that is not customarily provided to the public; or (2) Relinguish to, or otherwise provide, the government rights in excess of these rights customarily provided to the public to use, modify, reproduce, release, perform, display, or disclose commercial computer software or commercial computer software documentation. No additional government requirements beyond those set forth in the EULA shall apply, except to the extent that those terms, rights, or licenses are explicitly required from all providers of commercial computer software pursuant to the FAR and the DFARS and are set forth specifically in writing elsewhere in the EULA. Keysight shall be under no obligation to update, revise or otherwise modify the Software. With respect to any technical data as defined by FAR 2.101, pursuant to FAR 12.211 and 27.404.2 and DFARS 227.7102. the U.S. government acquires no greater than Limited Rights as defined in FAR 27.401 or DFAR 227.7103-5 (c), as applicable in any technical data.

# Warranty

THE MATERIAL CONTAINED IN THIS DOCUMENT IS PROVIDED "AS IS," AND IS SUBJECT TO BEING CHANGED, WITHOUT NOTICE, IN FUTURE EDITIONS. FURTHER, TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, KEYSIGHT DISCLAIMS ALL WARRANTIES, EITHER EXPRESS OR IMPLIED WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED

HEREIN, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MER-CHANTABILITY AND FITNESS FOR A PAR-TICULAR PURPOSE, KEYSIGHT SHALL NOT BE LIABLE FOR ERRORS OR FOR INCIDEN-TAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE. OR PERFORMANCE OF THIS DOCU-MENT OR ANY INFORMATION CONTAINED HEREIN. SHOULD KEYSIGHT AND THE USER HAVE A SEPARATE WRITTEN AGREE-MENT WITH WARRANTY TERMS COVER-ING THE MATERIAL IN THIS DOCUMENT THAT CONFLICT WITH THESE TERMS. THE WARRANTY TERMS IN THE SEPARATE AGREEMENT WILL CONTROL.

# Safety Notices

# **CAUTION**

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

# WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

# Obtaining Source Code

This product uses open source packages. To the extent required by the applicable open source license(s), Keysight makes source code available upon request. To request source code, contact Keysight Support at <a href="https://www.keysight.com/main/support.jspx">www.keysight.com/main/support.jspx</a>.

# Safety Summary

The following general safety precautions must be observed during all phases of operation of this instrument. Failure to comply with these precautions or with specific warnings or operating instructions in the product manuals violates safety standards of design, manufacture, and intended use of the instrument. Keysight Technologies assumes no liability for the customer's failure to comply with these requirements. Product manuals are provided with your instrument on CD-ROM and/or in printed form. Printed manuals are an option for many products. Manuals may also be available on the Web. Go to <a href="https://www.keysight.com">www.keysight.com</a> and type in your product number in the Search field at the top of the page.

#### General

This product is a Safety Class 1 instrument (provided with a protective earth terminal). The protective features of this product may be impaired if it is used in a manner not specified in the operation instructions.

All Light Emitting Diodes (LEDs) used in this product are Class 1 LEDs as per IEC 60825-1.

#### **Environment Conditions**

This instrument is intended for indoor use in an overvoltage category II, pollution degree 2 environment. It is designed to operate at a maximum relative humidity of 95% and at altitudes of up to 2000 meters.

Refer to the specifications tables for the ac mains voltage requirements and ambient operating temperature range.

#### Before Applying Power

Verify that all safety precautions are taken. The power cable inlet of the instrument serves as a device to disconnect from the mains in case of hazard. The instrument must be positioned so that the operator can easily access the power cable inlet. When the instrument is rack mounted the rack must be provided with an easily accessible mains switch.

#### Ground the Instrument

To minimize shock hazard, the instrument chassis and cover must be connected to an electrical protective earth ground. The instrument must be connected to the ac power mains through a grounded power cable, with the ground wire firmly connected to an electrical ground (safety ground) at the power outlet. Any interruption of the protective (grounding) conductor or disconnection of the protective earth terminal will cause a potential shock hazard that could result in personal injury.

# Do Not Operate in an Explosive Atmosphere

Do not operate the instrument in the presence of flammable gases or fumes.

#### Do Not Remove the Instrument Cover

Operating personnel must not remove instrument covers. Component replacement and internal adjustments must be made only by qualified personnel.

Instruments that appear damaged or defective should be made inoperative and secured against unintended operation until they can be repaired by qualified service personnel.

# Safety Symbols

Table 1 Safety Symbols

| Symbol   | Description                                                                                                                                                                                                   |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u> </u> | Indicates warning or caution. If you see this symbol on a product, you must refer to the manuals for specific Warning or Caution information to avoid personal injury or damage to the product.               |

| <i>/</i> | Frame or chassis ground terminal. Typically connects to the equipment's metal frame.                                                                                                                          |

|          | KC is the Korean certification mark to demonstrate that the equipment is Class A suitable for professional use and is for use in electromagnetic environments outside of the home.                            |

|          | Contains parts or assemblies susceptible to damage by electrostatic discharge (ESD). Use electrostatic discharge protective handling procedures to avoid malfunctions or potential damage to the instruments. |

| 40)      | Indicates the time period during which no hazardous or toxic substance elements are expected to leak or deteriorate during normal use. Forty years is the expected useful life of the product.                |

|          | The RCM Mark is a compliance mark to the ACMA (Australian Spectrum Management Agency). This indicates compliance with all Australian EMC regulatory information.                                              |

| c ⊕® US  | Indicates that the product was tested and has met the certification requirements for electrical, plumbing and/or mechanical products.                                                                         |

Symbol Description

The CE mark is a registered trademark of the European Community. This CE mark shows that the product complies with all the relevant European Legal Directives.

CAN ICES/NMB-001(A) - This ISM device complies with the Canadian ICES-001(A).

Cet appareil ISM est conforme a la norme NMB-001(A) du Canada.

ISM GRP 1-A - This is an Industrial Scientific and Medical (ISM) Group 1 Class A product.

This symbol on all primary and secondary packaging indicates compliance to China standard GB 18455-2001.

# Compliance and Environmental Information

Table 2 Compliance and Environmental Information

# The crossed out wheeled bin symbol indicates that separate collection for waste electric and electronic equipment (WEEE) is required, as obligated by DIRECTIVE 2012/19/EU and other National legislation. See <a href="http://about.keysight.com/en/companyinfo/environment/takeback.shtml">http://about.keysight.com/en/companyinfo/environment/takeback.shtml</a> to understand your Trade in options with Keysight in addition to product takeback instructions.

#### About This Guide

Here is how the information in this document is organized.

#### Introduction

This chapter provides an overview of this manual.

#### **Know Your Hardware**

This chapter provides an information on the various modules of M8020A/M8040A/M8050A, their setup and the provided accessories.

#### **Exploring M8070B User Interface**

This chapter describes the M8070B user interface and the functionality provided by its common GUI elements.

#### **Configuring Your System**

This chapter describes how to configure the M8020A/M8040A/M8050A system using the Module View, Group View and System View.

#### Setting up Generator

This chapter provides information on settings provided by the M8020A/M8040A/M8050A Generator

#### Setting up Analyzer

This chapter provides information on settings provided by the M8020A/M8040A/M8050A Analyzer.

#### **Setting up Patterns**

This chapter describes the functionality provided by the M8070B Pattern Editor and Sequence Editor.

#### Working with Measurements

This chapter describes the setup, execution, monitoring and results of the measurements supported by M8070B system software.

#### Utilities

This chapter describes the utilities provided by the M8070B system software.

#### Licenses

This chapter provides information on the M8020A/M8040A/M8050A and M8070B licenses and their installation procedure.

#### **Appendix**

This chapter provides information about basic troubleshooting and factory patterns.

# Contents

Obtaining Source Code 3

Safety Summary 4

Safety Symbols 5

Compliance and Environmental Information

About This Guide 8

#### 1 Introduction

Overview 28

M8020A High-Performance BERT 28

M8040A High-Performance BERT 29

M8050A High-Performance BERT 120 GBd 31

Document History 33

Related Documents 34

Abbreviations used in this Document 35

# 2 Know Your Hardware

M8020A Overview 38

M9505A AXIe Chassis 39

AXIe Embedded System Module (USB ESM) 40

M9506A AXIe Chassis 40

Host Computer 43

Keysight M9537A AXIe Embedded Controller Module 43

#### **M8020A Modules** 45

J-BERT M8041A Generator-Analyzer-Clock Module 45

M8041A Front Panel Connector Inputs/Outputs 48

J-BERT M8051A Generator-Analyzer 50

M8062A 32Gb/s Front-end for J-BERT M8020A High-Performance

BERT 53

M8062A Features 53

M8062A Module Components 54

M8062A Front Panel Pattern Generator Connectors 55

M8062A Front Panel Analyzer Connectors 56

# M8020A Module Setup 57

Setting up a Single Channel System 57 Setting up a Multi-Channel System 57

M8040A Overview 59

**M8040A Modules** 60

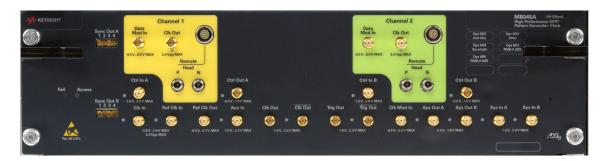

M8045A High-Performance BERT Pattern Generator-Clock Module 60

M8046A High-Performance BERT Analyzer Module 64

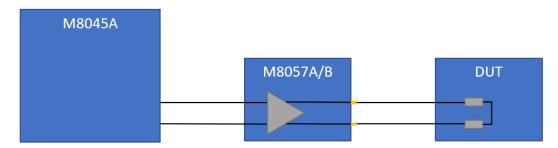

M8057A/B Pattern Generator Remote Head 66

M8040A Module Setup 69

**M8050A Overview** 70

**M8050A Modules** 71

M8042A Pattern Generator 71 M8009A Clock Generator 74

M8058A/M8059A Remote Head for M8042A Pattern Generator 77

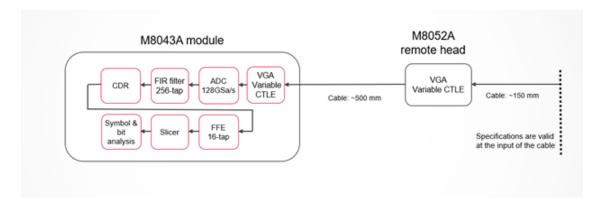

M8043A Error Analyzer 79

M8043A Front Panel Input/Output Ports 81

M8052A Remote Head for M8043A Error Analyzer 82

M8052A Remote Head Components 82

M8050A Module Setup 84

| M8070B Supported Plugins 86                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>M8100 Series Arbitrary Waveform Generators</b> 87                                                                                                                                                                                                                       |

| M8199A 128/256 GSa/s Arbitrary Waveform Generator M8199B 256 GSa/s Arbitrary Waveform Generator M8008A Clock Generator 89 M8194A 120 GSa/s Arbitrary Waveform Generator 90 M8195A 65 GSa/s Arbitrary Waveform Generator 91 M8196A 92 GSa/s Arbitrary Waveform Generator 92 |

| M8054A Interference Source Module 93                                                                                                                                                                                                                                       |

| Key Features & Specifications 93                                                                                                                                                                                                                                           |

| M8047A PCI Express Re-driver 94                                                                                                                                                                                                                                            |

| Key Features 94                                                                                                                                                                                                                                                            |

| M8047B PCI Express Re-driver 95  Key Features 95                                                                                                                                                                                                                           |

| Other Supported Hardware(s) 96                                                                                                                                                                                                                                             |

| Keysight N1076A/N1076B/N1077A DCA-M Clock Recovery 96 Keysight Real Time Oscilloscopes 98 DCA models supported for deemphasis optimization tool 101                                                                                                                        |

|                                                                                                                                                                                                                                                                            |

| Hardware Setup for M8046A and M8062A Modules 104 Limitations 105                                                                                                                                                                                                           |

| <b>ESD Protection</b> 106                                                                                                                                                                                                                                                  |

## 3 Quick Tour with M8070B User Interface

#### Overview 112

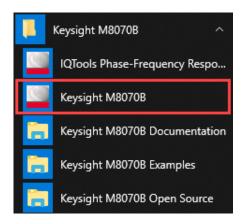

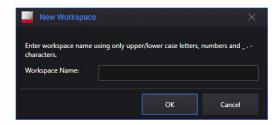

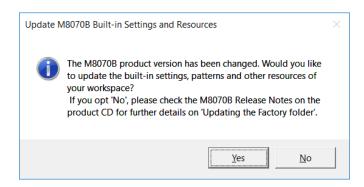

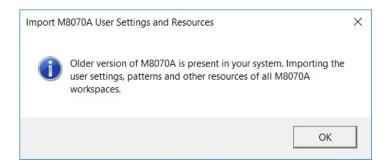

# **Launching M8070B User Interface** 113

Starting M8070B on the command line 120

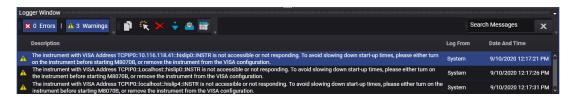

Messages while launching M8070B GUI 122

Load Setting 123

Get Module Information 126

## **Exploring M8070B User Interface** 127

Title Bar 127 Menu Bar 127 Main Window 145 Status Bar 146

#### Other GUI Features 150

#### Recall/Save Instrument State 158

Recall Instrument State 158

Save Instrument State 160

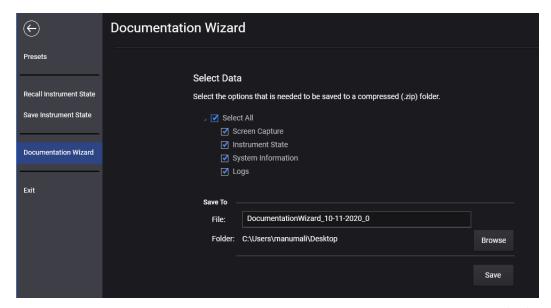

**Documentation Wizard** 161

# 4 User Interface - M8070B Display Views

#### Overview 164

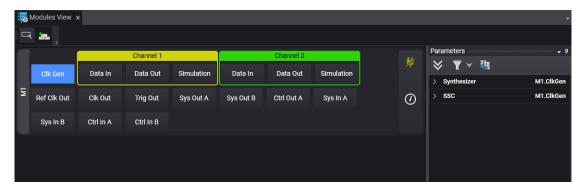

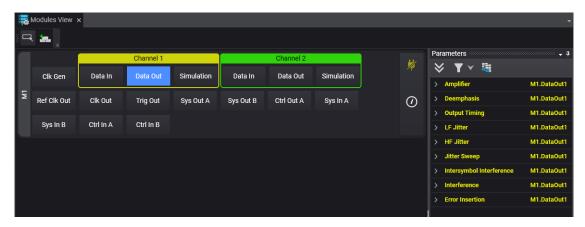

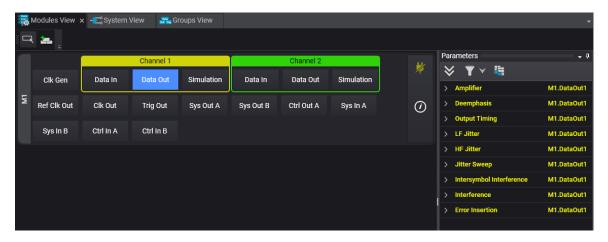

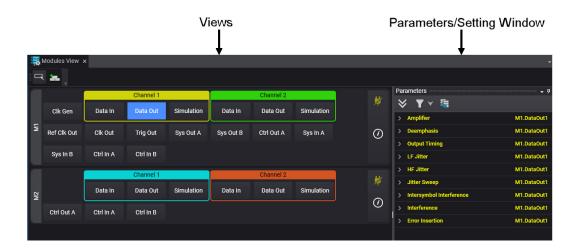

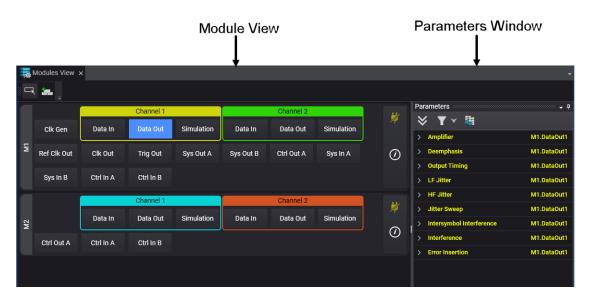

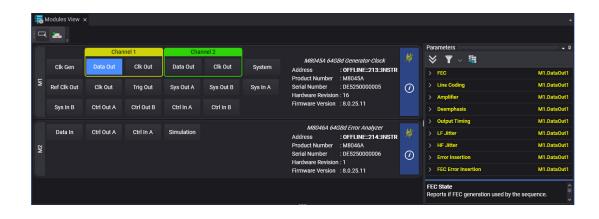

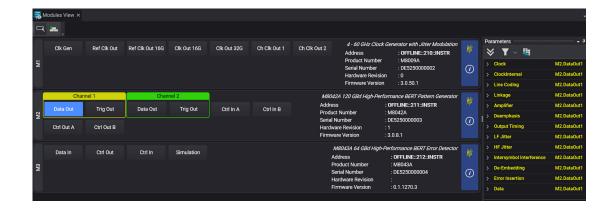

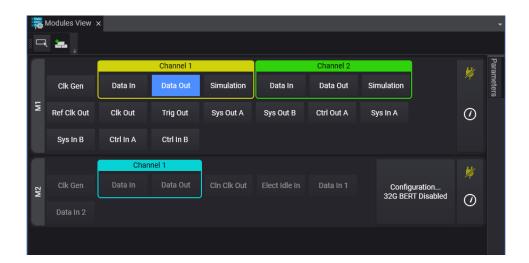

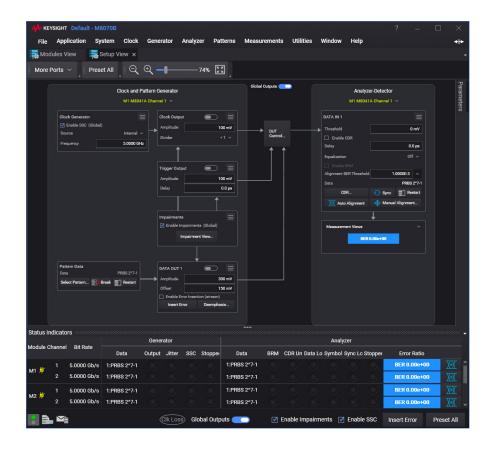

#### Module View 165

How to Launch Module View 165

Input and Output Ports 168

Show Module Information 174

Selecting Single/Multiple Ports 174

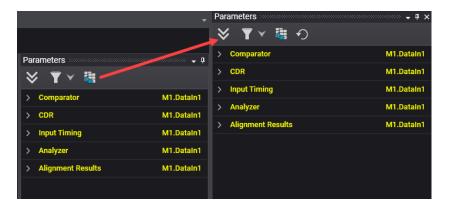

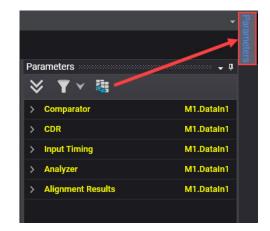

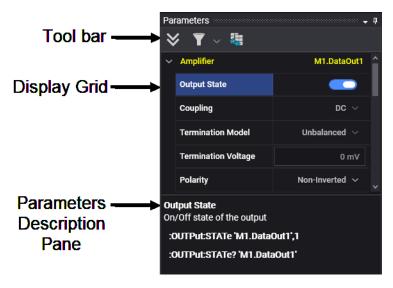

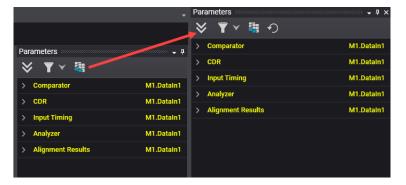

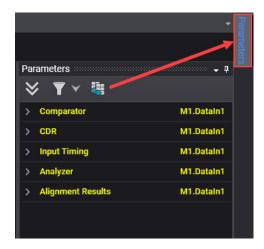

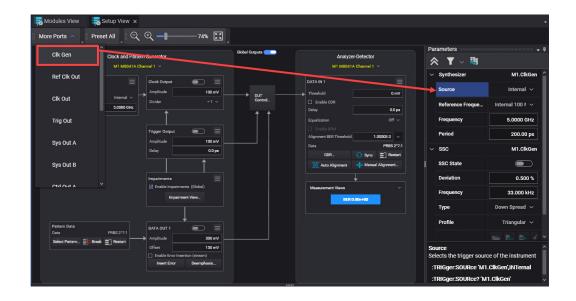

Parameters Window 175

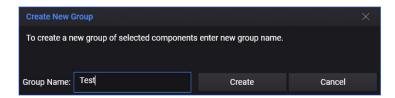

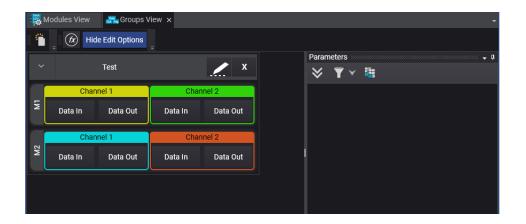

Creating Groups in the Module View 194

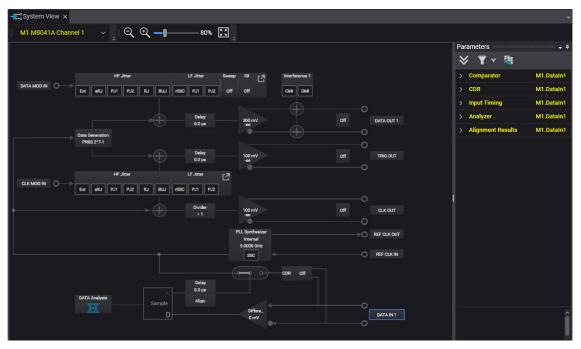

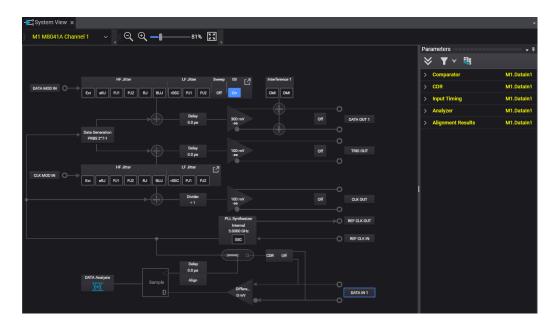

## System View 195

Using the Zoom Tool 196

Understanding the System View 197

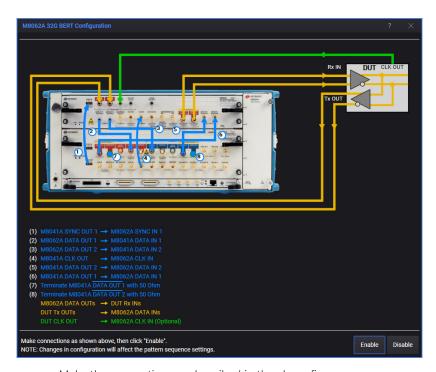

System View with M8062A Integration 201

M8040A System View 205

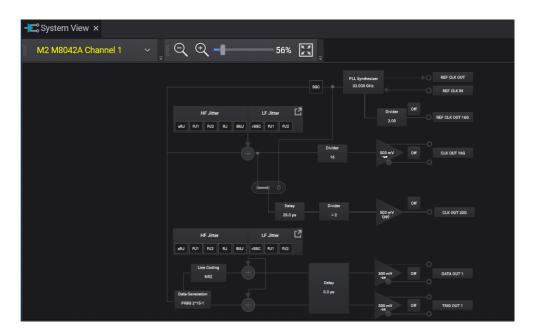

M8050A System View 207

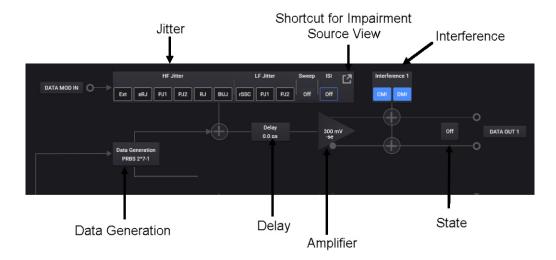

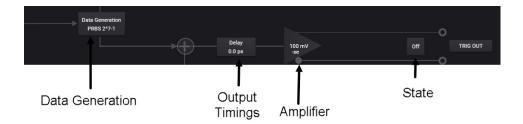

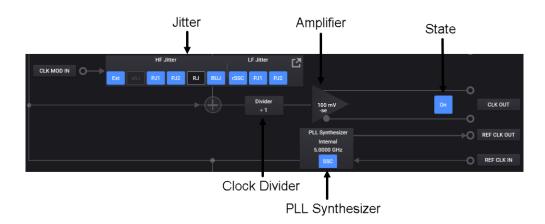

## Impairment Setup View 208

How to Access the Impairment Setup View 208

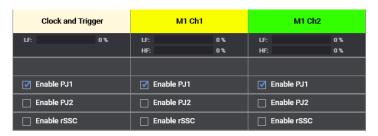

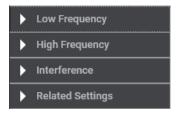

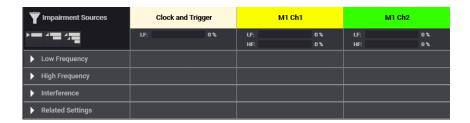

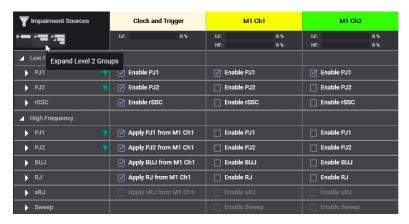

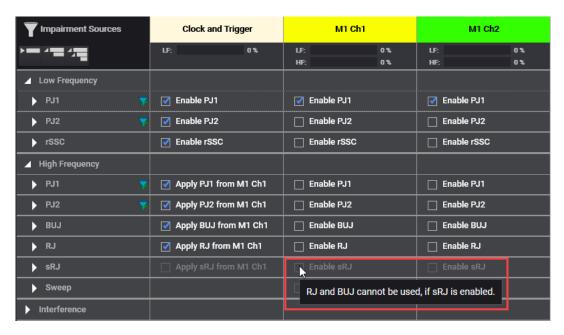

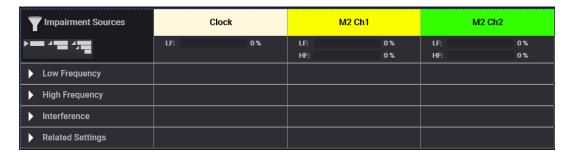

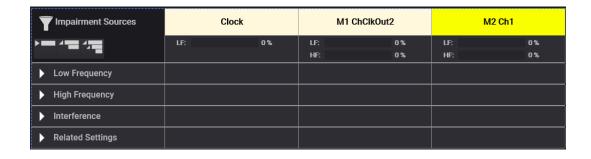

Features of the Impairment Setup View 209

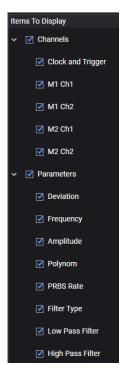

Viewing Options in the Impairment Setup View 211

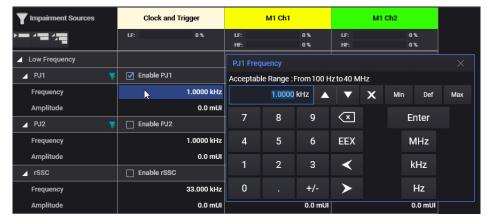

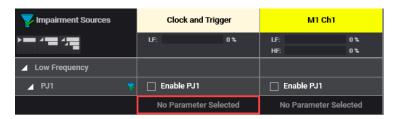

How to set parameters in Impairment Setup View 213

How to Use Filters 216

Impairment Setup View Support by the M8050A System 218

#### Group View 220

How to Launch Group View 220

#### Setup View 226

How to Access the Setup View 226

Understanding Setup View 227

GUI Elements Description 230

How to perform a basic measurement 232

# Controlling M8194A, M8195A, and M8196A AWG(s) from M8070B User Interface 233

AWG(s) in Module View 233

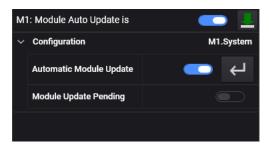

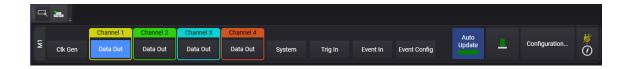

Automatic Module Update in AWG(s) 234

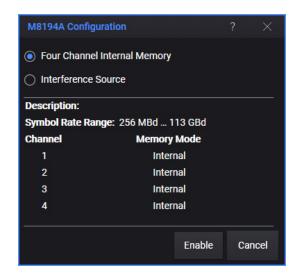

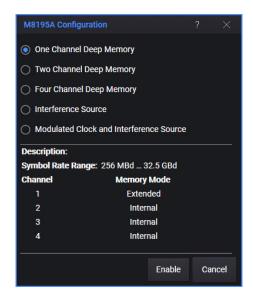

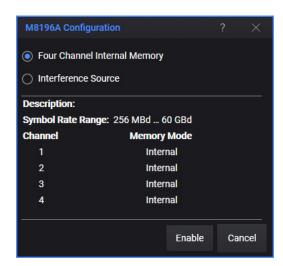

M819xA Configuration 236

Configuring AWG(s) Parameters 239

Simultaneous Injection of RI and SI Using M819xA AWGs on Same

Channel 250

Simultaneous Injection of RI and SI Using M819xA AWGs on Different

Channels 253

| Simultaneous Injection of CMSI and DMSI Using M819xA AWGs Simultaneous Injection of CMRI or DMRI Using M819xA AWGs Simultaneous Injection of CMRI with CMSI Using M819xA AWGs Simultaneous Injection of CMRI with DMSI Using M819xA AWGs Simultaneous Injection of DMRI with CMSI Using M819xA AWGs Simultaneous Injection of DMRI with DMSI Using M819xA AWGs Simultaneous Injection of DMRI with DMSI Using M819xA AWGs AWG as External Level Interference (RI/SI) Source 270 System View with AWG(s) Integration 271 Signal Generation in AWG 272 Using AWG Frequency Response Calibration for Improved Signal Performance 273 M8194A amplitude behavior using (de-)embedding 273 Selecting Line Coding 274 Creating Patterns for AWG(s) 277 Sequence Settings for AWG(s) 279 | 256<br>261<br>266<br>267<br>268<br>269 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Controlling M8054A from M8070B System Software 281  M8054A in Module View 281  Simultaneous Injection of RI and SI Using M8054A on Same Channel 287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                        |

| Channel 287 Simultaneous Injection of RI and SI Using M8054A on Different Channels 290                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                        |

| Simultaneous Injection of CMSI and DMSI Using M8054A 293 Simultaneous Injection of CMRI or DMRI using M8054A 297 Simultaneous Injection of CMRI with CMSI Using M8054A 301 Simultaneous Injection of CMRI with DMSI Using M8054A 302 Simultaneous Injection of DMRI with CMSI Using M8054A 303 Simultaneous Injection of DMRI with DMSI Using M8054A 304 M8054A as External Level Interference (RI/SI) Source 305 System View of M8054A 306                                                                                                                                                                                                                                                                                                                                      |                                        |

# Controlling M8047A PCI Express Re-driver from M8070B User Interface 307

M8047A in Module View 307

M8047A Parameters configuration 308

# Controlling M8047B PCI Express Re-driver from M8070B User Interface 309

M8047B in Module View 309

M8047B Parameters configuration 310

# **Extended Sequencing Capabilities in AWGs** 311

Basic Sequencing 311

Extended Sequencing 31

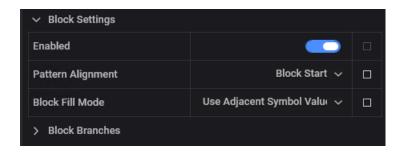

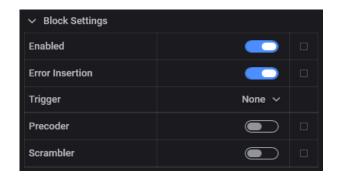

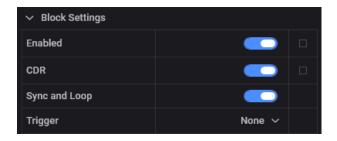

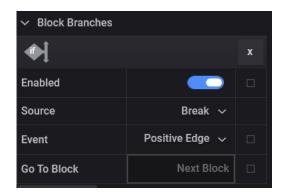

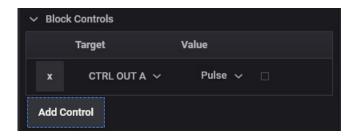

Block Settings 313

Event Configuration 315

SCPI Commands 315

# 5 Setting up Generator

Overview 318

**M8020A Generator Ports** 319

M8040A Generator Ports 321

M8050A Generator Ports 323

# **Understanding Pattern Generator Features** 325

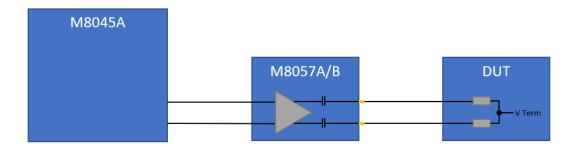

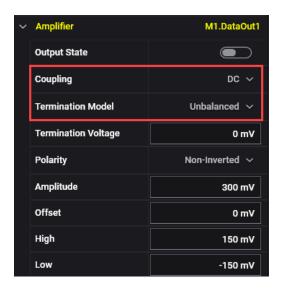

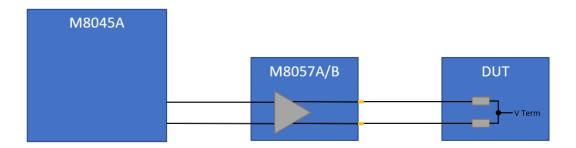

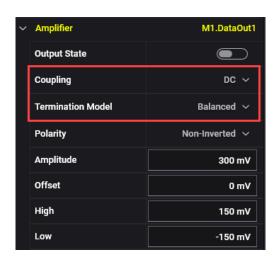

Output Termination Modes of M8045A with M8057A/B

Understanding the Output Protection Circuit 328

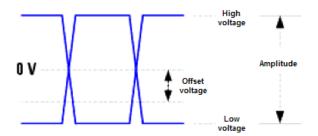

Understanding the Output Level Parameters 329

Why Incorrect Terminations Could Damage Your Device 331

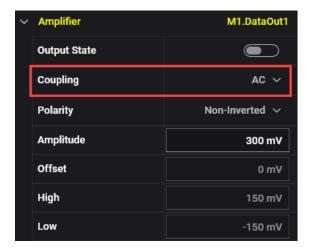

M8020A/M8040A/M8050A AC Coupling and Bias Tees 322

Setting up Terminations 334

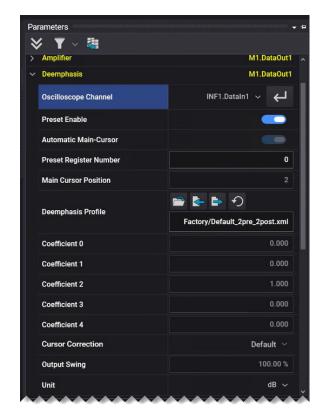

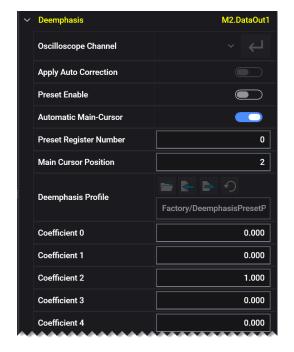

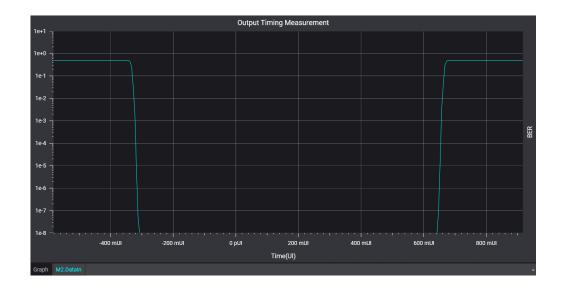

DC Check (Unbalanced/Balanced Termination) for M8020A/M8040A/M8050A 335 Adjust Output Levels (optional) 338 Deemphasis Signal Generator 339 342 M8070B Factory Deemphasis Profiles M8020A Deemphasis 343 M8045A Deemphasis 344 347 M8040A Automatic Pattern Generator Deemphasis M8050A Automatic Pattern Generator Deemphasis 356 359 Setting Up Data Out Port Parameters Setting up Output Timing 361

#### Bit Rate 363

When to Use an External Clock Source? 363

Bit Rate Range 363

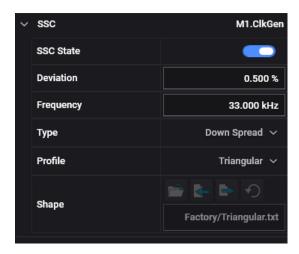

Spread Spectrum Clocking 365

Setting the Bit Rate 366

External Clock Divider 367

External PLL Clock Divider and Multiplier 367

Trigger Output 368

**Error Insertion** 371

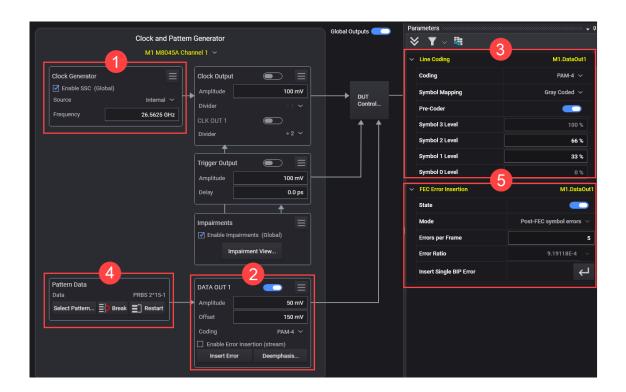

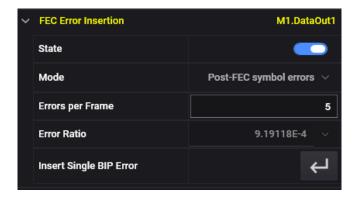

**FEC Error Insertion** 373

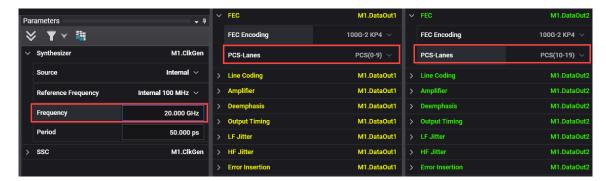

**FEC Encoding** 377

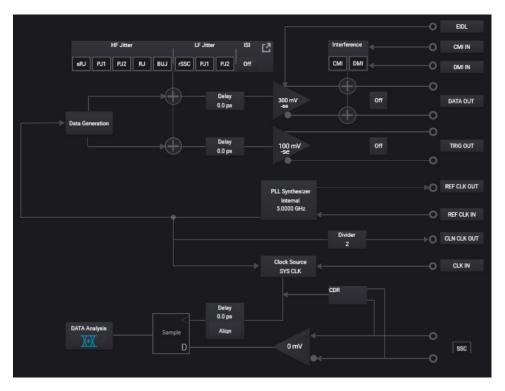

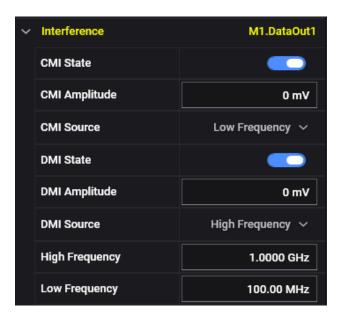

Interference 379

Common Mode Interference (CMI) 379

Differential Mode Interference (DMI) 380

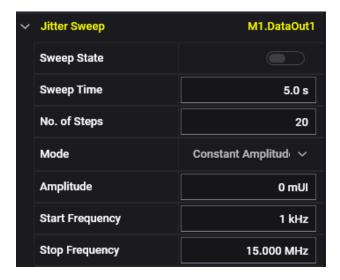

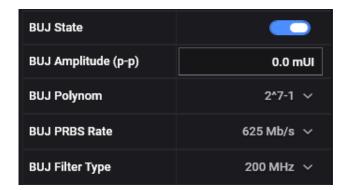

# Jitter Setup 381

High Frequency Jitter (HF Jitter) 381

Low Frequency Jitter (LF Jitter) 381

How to Enable Global Jitter State 381

Set Jitter Configuration 382

#### Idle Pattern 393

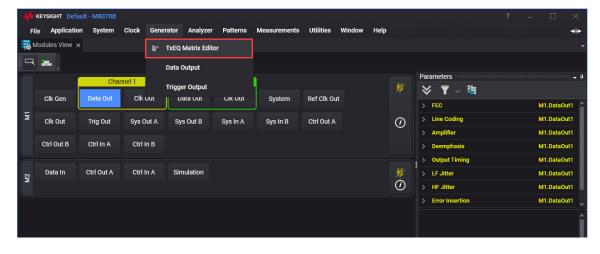

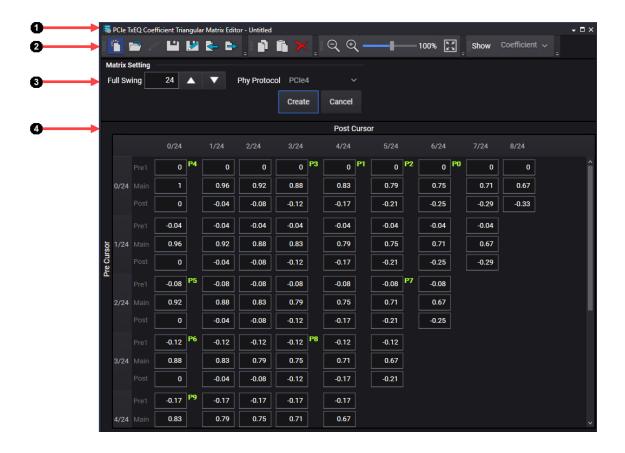

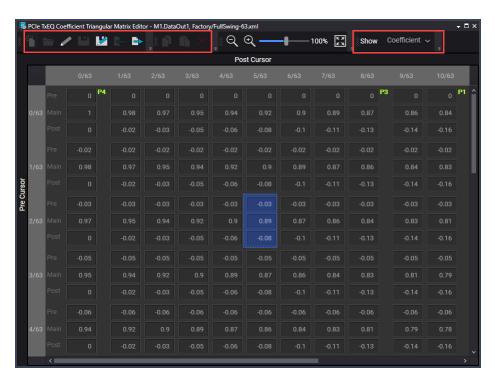

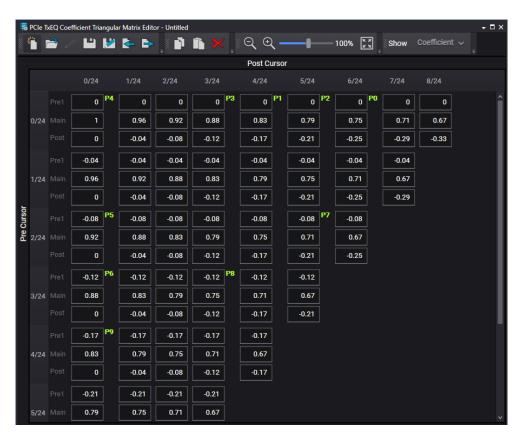

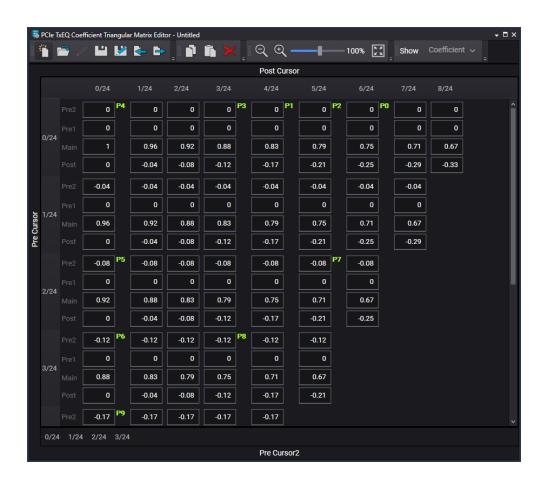

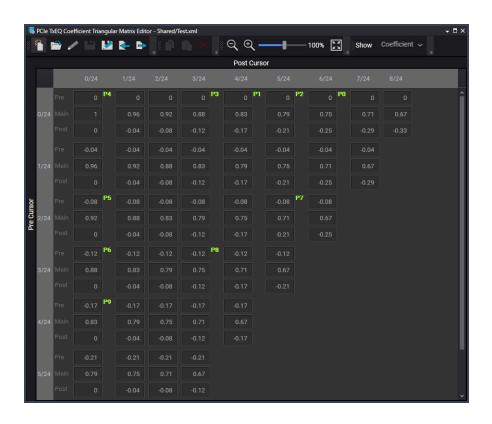

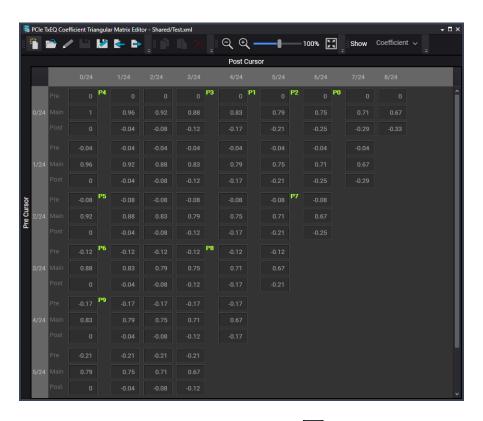

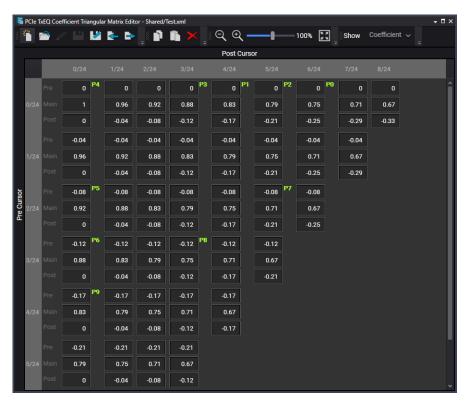

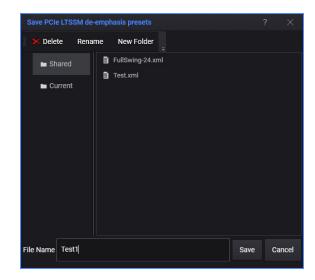

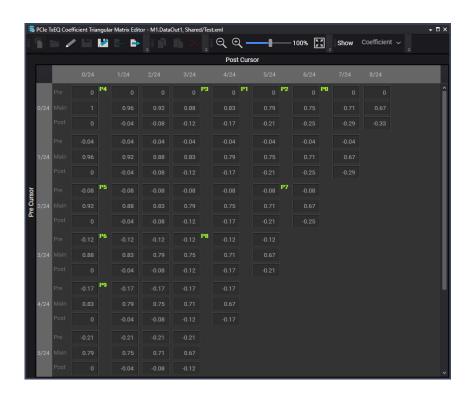

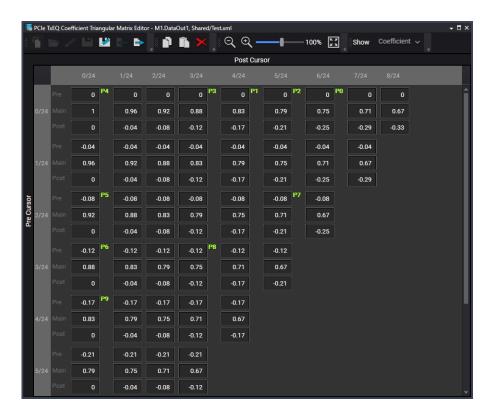

#### **TxEQ Matrix Editor** 394

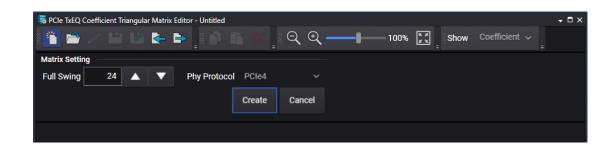

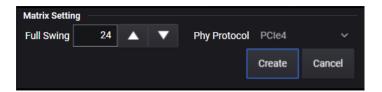

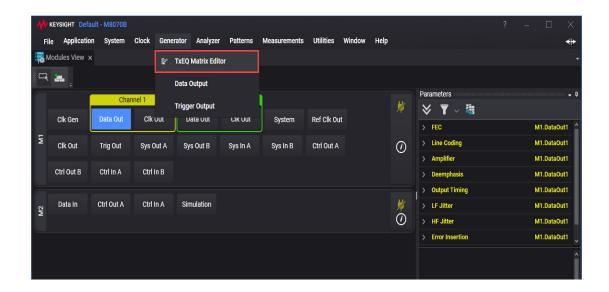

Launching the TxEQ Matrix Editor 394

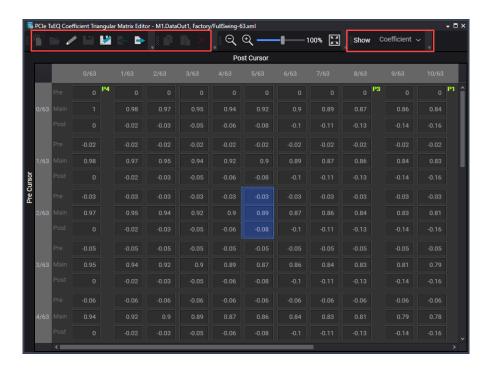

Exploring the TxEQ Matrix Editor User Interface 398

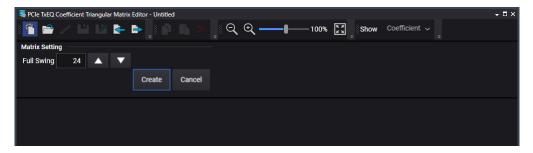

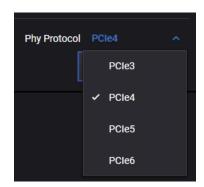

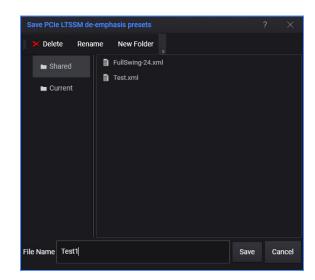

Creating a new matrix 404

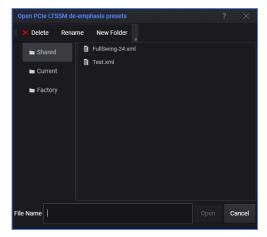

Opening an existing matrix 410

Editing an existing matrix 412

Importing a matrix file 421

Exporting a matrix file 423

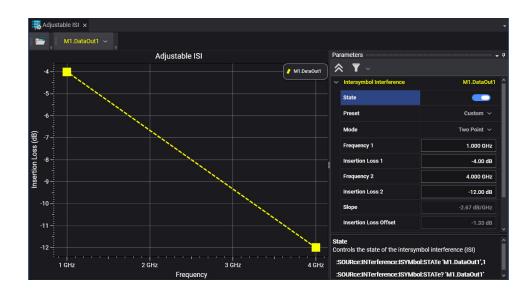

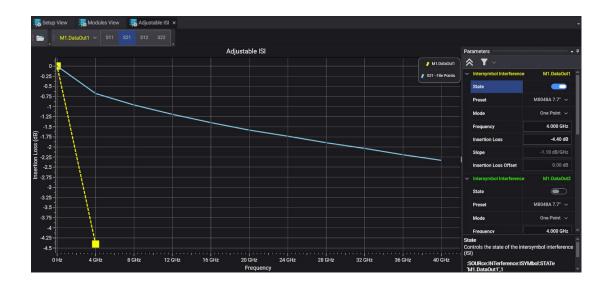

# Adjustable Intersymbol Interference 425

Using System View for ISI Configuration 425

How to Launch Adjustable ISI Window: 426

Toolbar 428

Adjustable ISI Graph 428

ISI Parameters 429

Intersymbol Interference (ISI) Setup 429

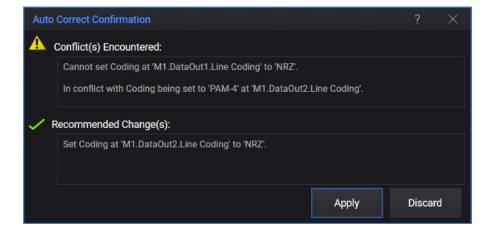

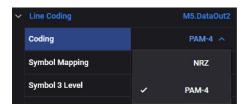

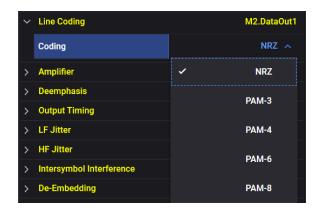

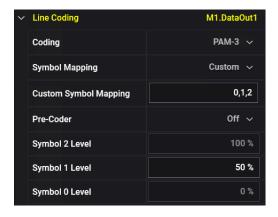

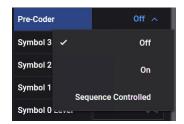

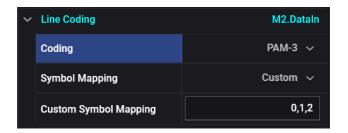

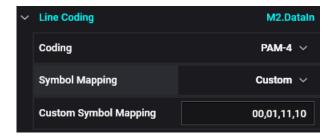

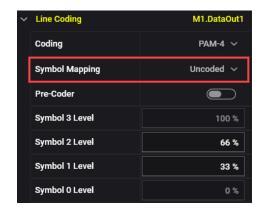

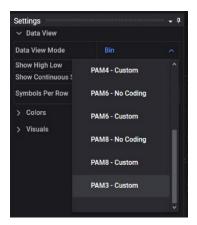

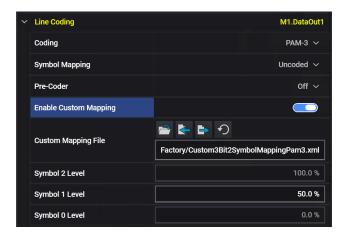

# Line Coding 431

PAM3 Line Coding 432

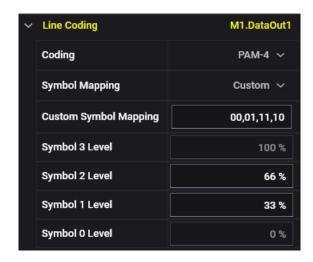

PAM4 Line Coding 437

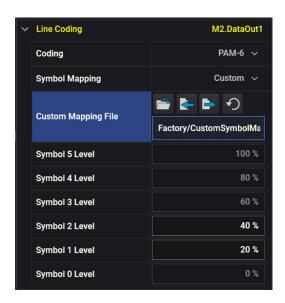

PAM6/PAM8 Line Coding 438

# Segmented SSC Profile using M8009A Clock Module 444

Segmented SSC Configuration 446

Segmented SSC Parameters 447

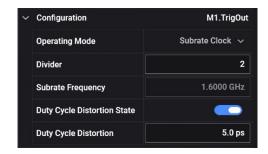

Configuring Trigger Output on System Module (ESM) 449

# 6 Setting up Analyzer

#### Overview 452

# M8020A/M8040A/M8050A Analyzer Ports 453

Data In Port Termination 454

Why Can Wrong Terminations Damage Your Device? 455

Setting Up Termination 455

Data Inverted 460

Threshold 460

PAM4 Decision Threshold 460

Termination Voltage 461

Input Range 461

Squelch Threshold 462

Input Sensitivity 463

# Clock Setup 464

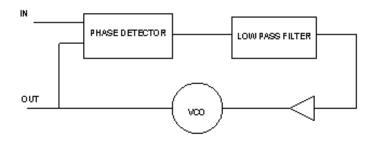

How does Clock Data Recovery Work? 464

Phase Locked Loop 464

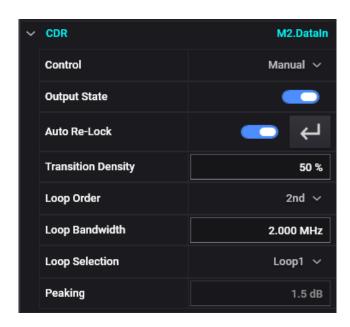

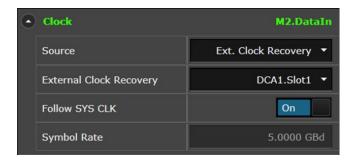

CDR Setup for M8020A 466

CDR Setup for M8040A 467

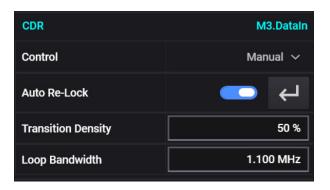

CDR Setup for M8050A 470

# Pattern Synchronization 472

Introduction to Pattern Synchronization 472

What Type of Synchronization Should You Use? 475

What is False Synchronization? 476

How Can You Tell if Your Synchronization is False? 477

How to Synchronize an Incoming Pattern 479

# Bit Recovery Mode 480

Understanding Bit Recovery Mode (BRM) 480

Setting up Bit Recovery Mode 481

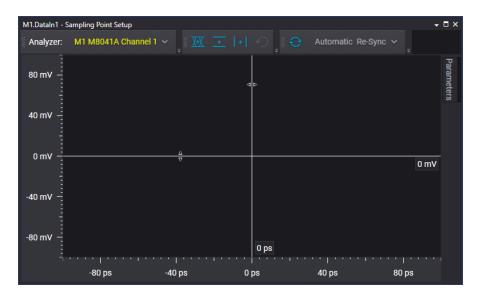

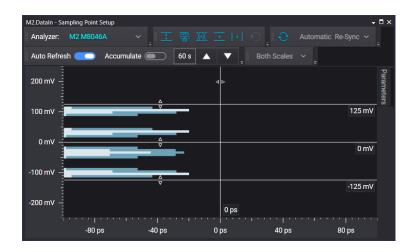

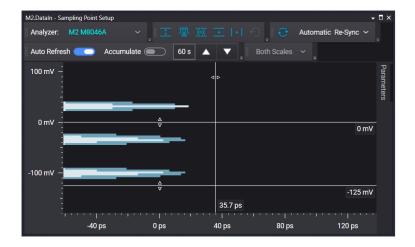

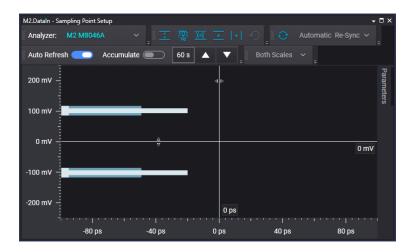

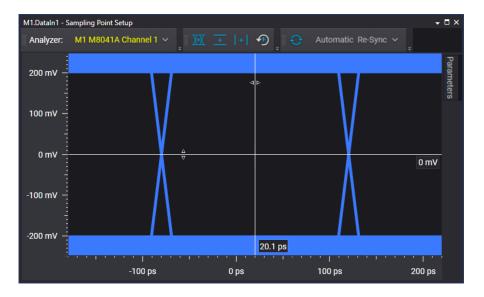

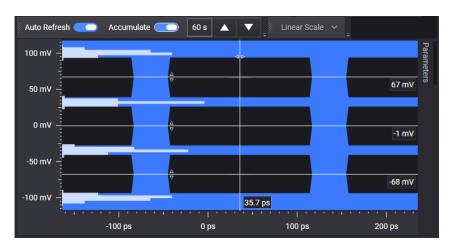

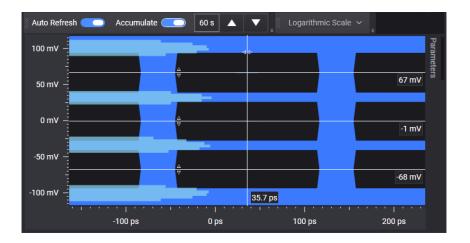

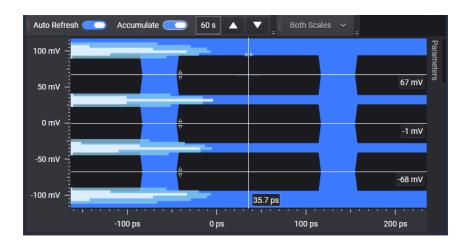

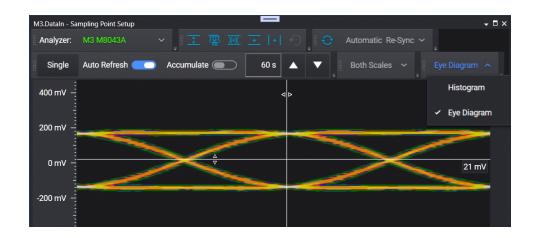

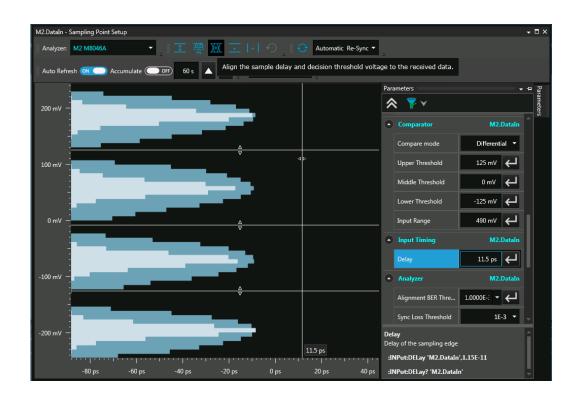

# Sampling Point Setup 482

How Does the Sampling Point Setup Work? 482

Auto Alignment 482

Threshold Center Alignment 483

Delay Center Alignment 484

Canceling Auto Align 485

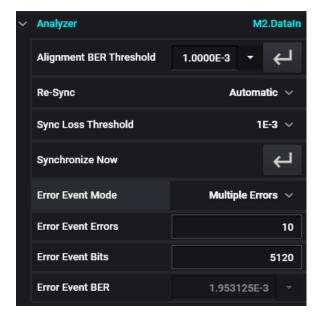

Alignment BER Threshold 485

Sampling Point Setup Window 485

Line Coding 497

Error Event Mode 499

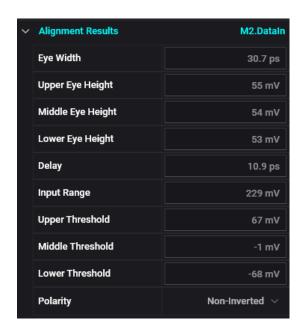

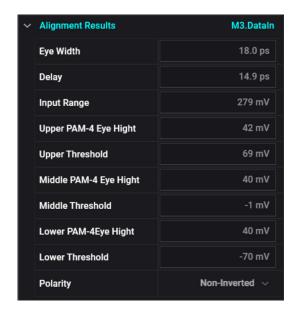

#### Alignment Results 501

Alignment Results for M8020A/M8040A 501 Alignment Results for M8050A 504

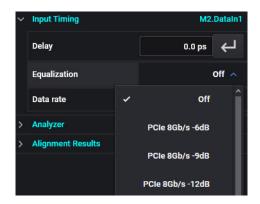

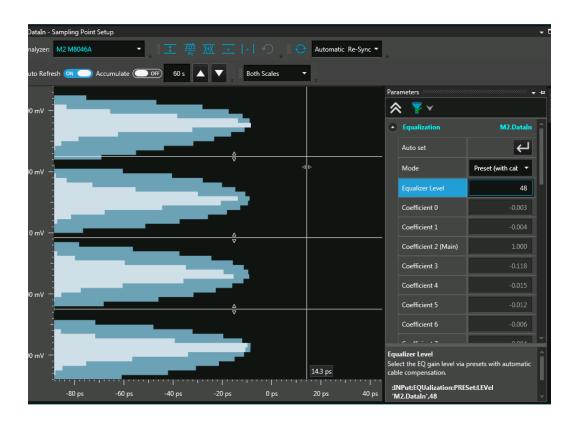

# **Equalization** 506

Equalization in M8041A/M8051A Data In 506

Equalization in M8062A Data In 507

Equalization in M8046A Data In 508

Equalization in M8043A Data In 522

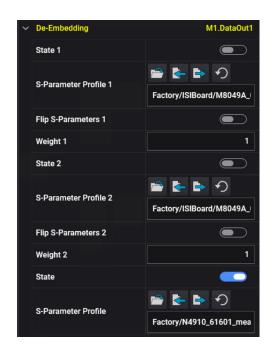

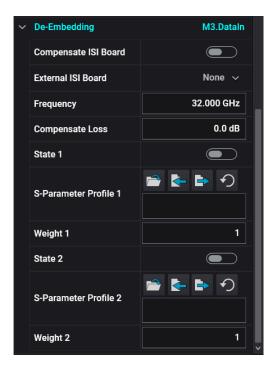

De-Embedding 524

# 7 Setting up Patterns

Pattern Overview 528

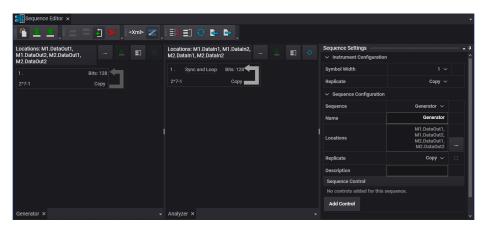

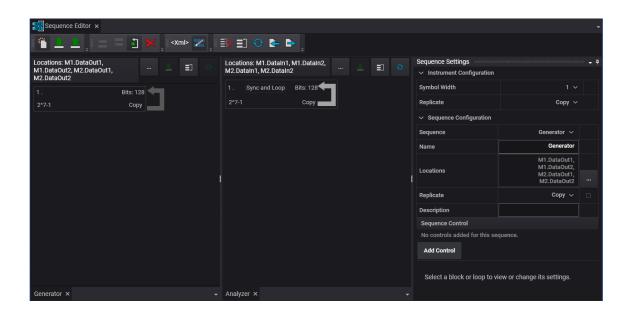

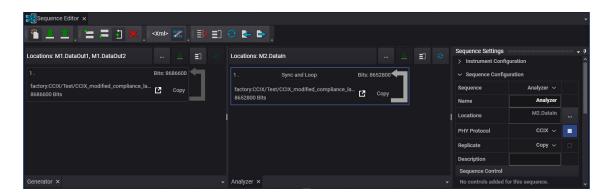

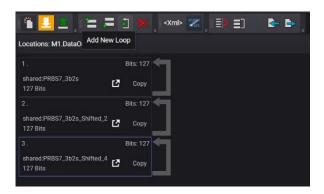

Sequence Editor 529

Overview 529

When to Use a Sequence 529

How a Sequence is Defined 529

How to Launch a Sequence Editor 530

Toolbar 531

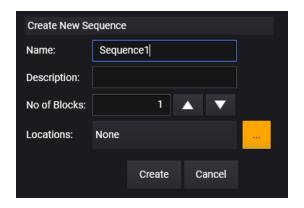

Creating New Sequence 532

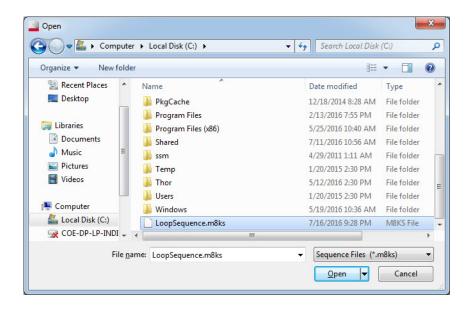

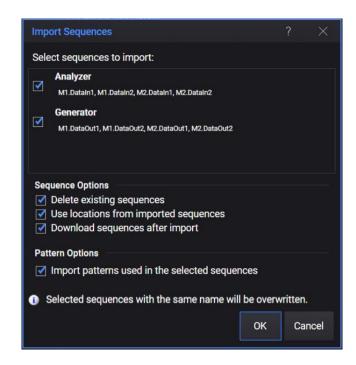

Importing a Sequence 533

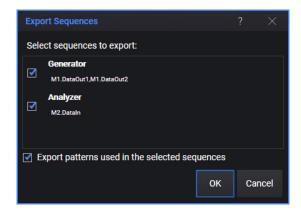

Exporting a Sequence 535

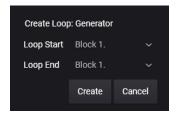

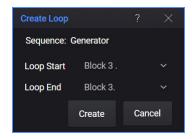

Creating a Loop 535

Loop Within Sequences 536

Modifying the Existing Sequences 536

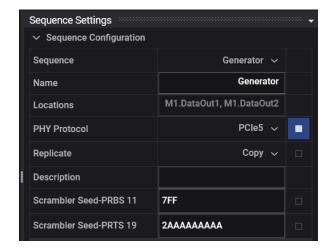

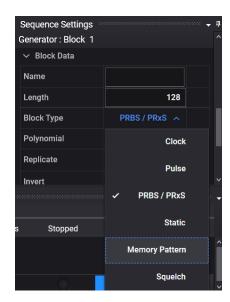

Sequence Setting Window 537

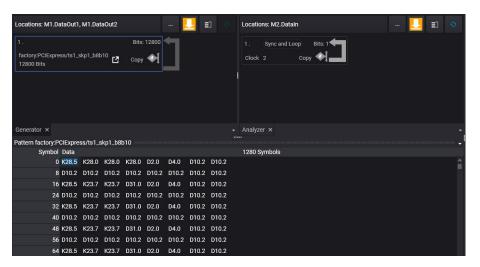

Editing a Pattern in a Sequence Editor 559

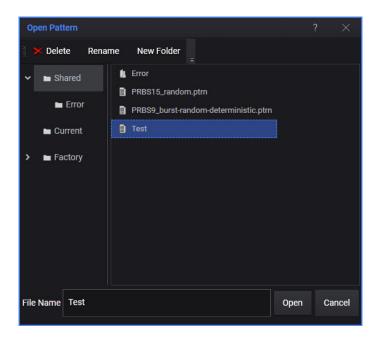

Sharing Sequences 560

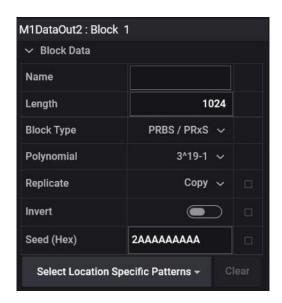

**User-Defined Sequences** 561

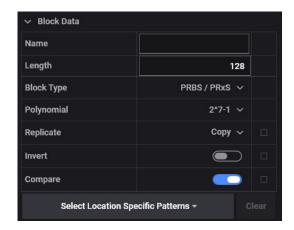

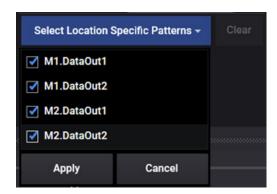

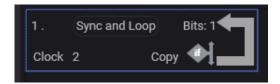

Sequence Block Display 561

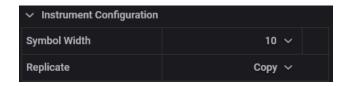

Sequence Block Parameters 561

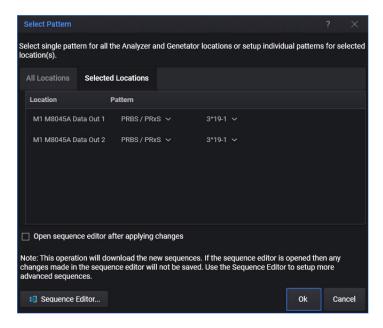

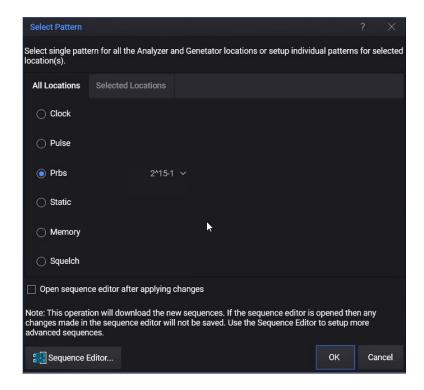

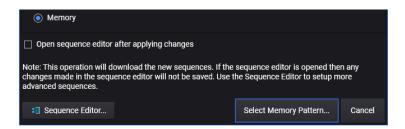

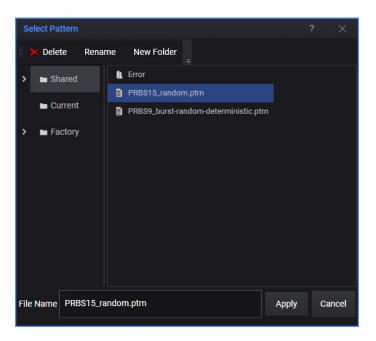

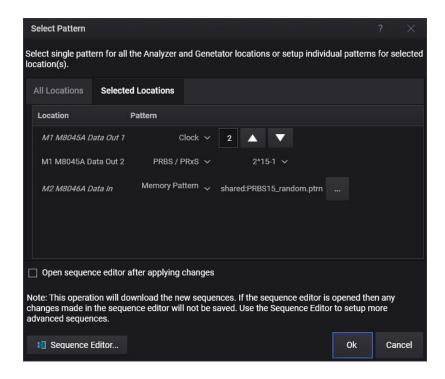

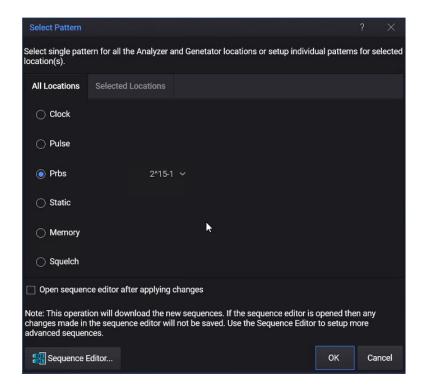

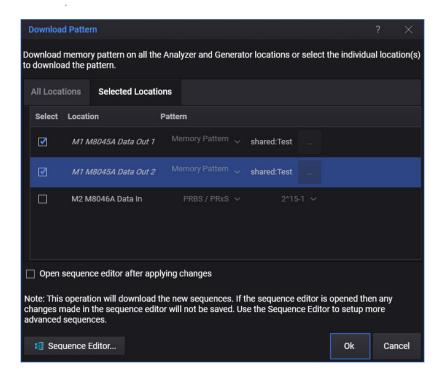

Select Pattern Dialog 562

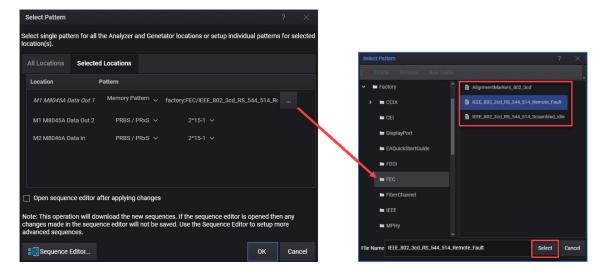

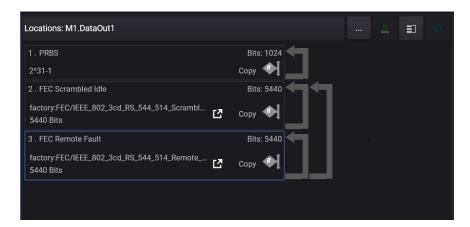

**Application Specific Patterns** 566

OIF CEI 566

IEEE 802.3 566

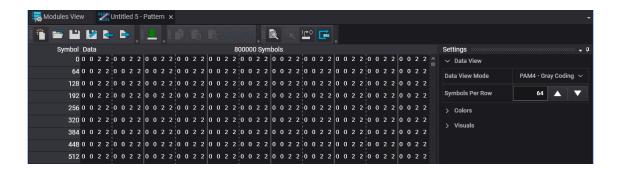

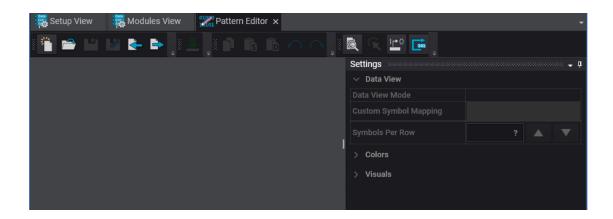

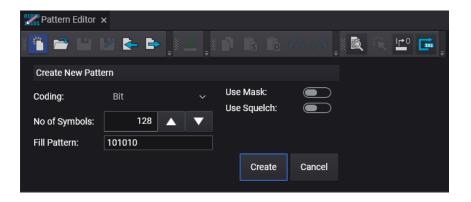

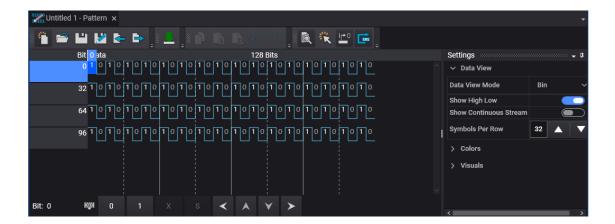

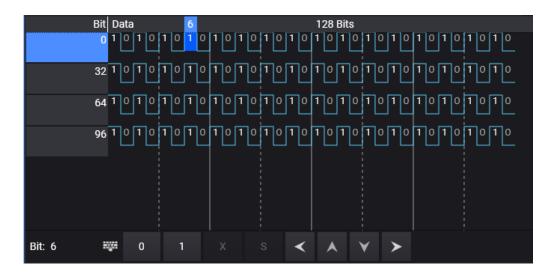

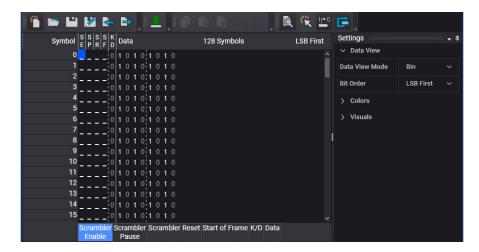

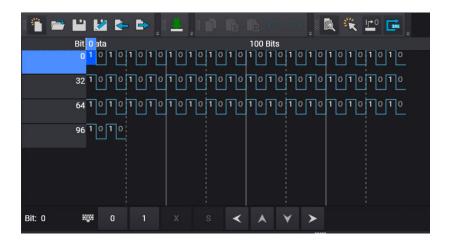

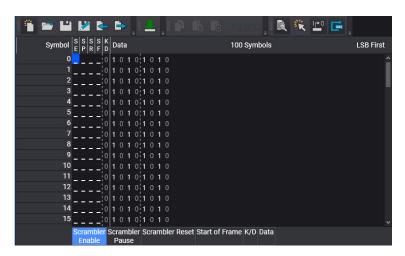

#### Pattern Editor 568

How to Launch Pattern Editor 568

Toolbar 569

Settings Window 585

Pattern Edit Pane 587

Bit Coding 592

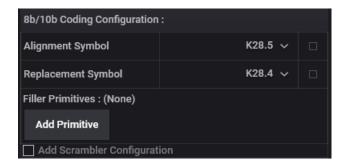

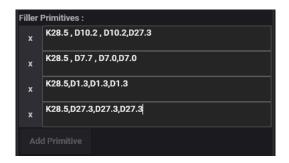

8B/10B Coding 594

128B/130B Coding 596

128B/132B Coding

#### Pattern Capture 601

How to Launch Pattern Capture Window 601

598

Toolbar 602

Parameters Window 603

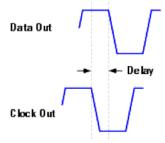

How to Capture a Pattern 605

Pattern Capture Pane 606

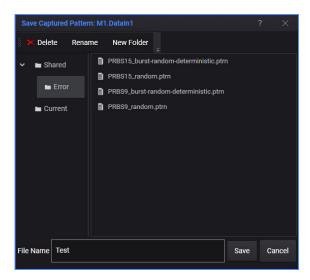

Saving a Captured Pattern 607

Capture Results Pane 608

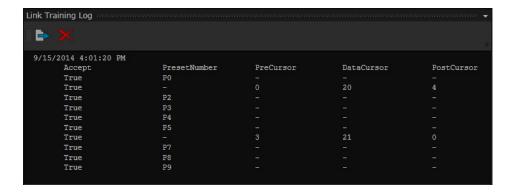

# **Interactive Link Training** 609

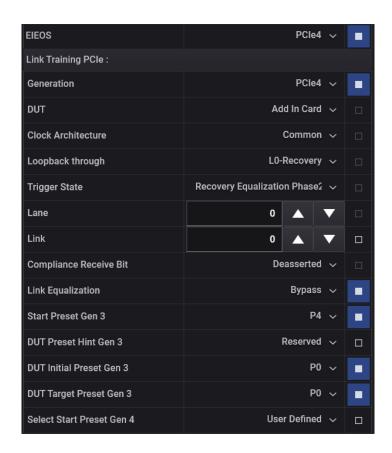

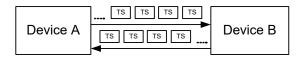

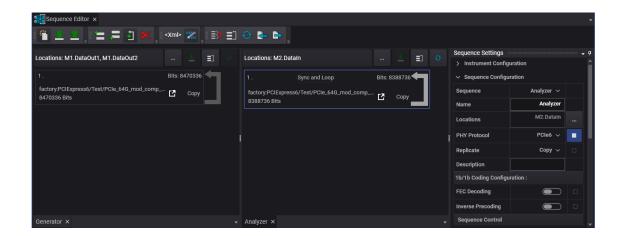

PCI Express 3.0/4.0 Testing 609

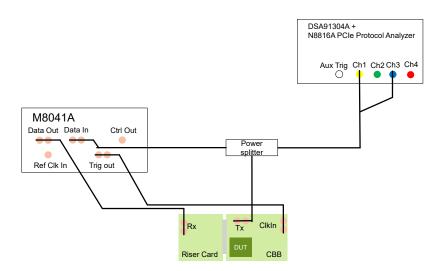

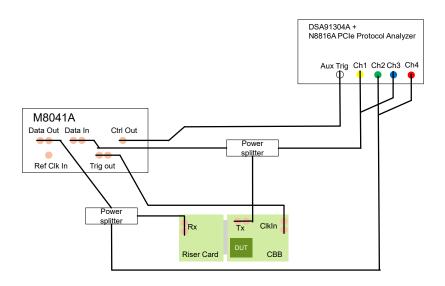

M8070B support for PCle3.0/4.0 link training using M8020A 614

M8070B support for USB 3.2 Gen 1/USB 3.2 Gen 2 link training using

M8020A/M8040A 617

M8070B Support for PCle3.0/4.0/5.0/6.0 Link Training using

M8040A/M8050A 631

# **Using M8062A Data Out Squelch Feature** 650

Limitations 650

Hardware Requirements 650

Hardware Setup 650

Software Usage 650

## M8046A PHY Protocol Selection (SKP OS Filtering) 654

PHY Protocol 654

SKP Ordered Set filtering/removal 656

Setting up SKP OS filtering 657

1b/1b Coding Configuration for PCle6 658

Setting up SKP OS filtering for PCle6 660

## Using Pattern Shift and 3b2s Mapping in M8070B 662

# 8 Working with Measurements

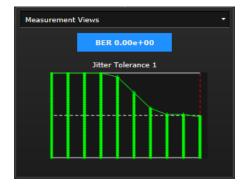

#### Overview 668

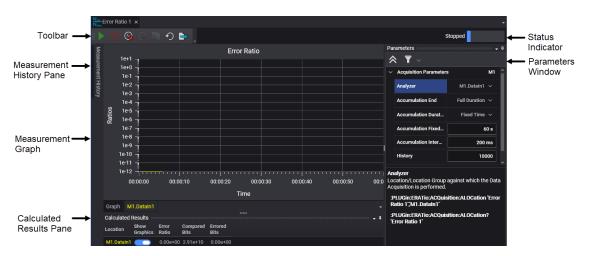

## **Exploring Measurement User Interface** 669

Launching the Measurement User Interface 669

Toolbar 670

Status Indicator 671

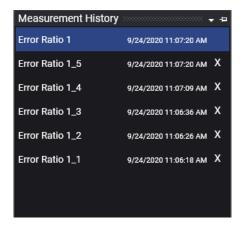

Measurement History Window 671

Copy Measurement History Properties 672

Measurement Graph 672

Parameters Window 674

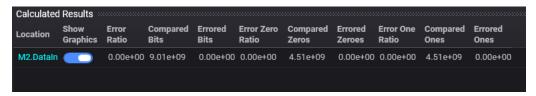

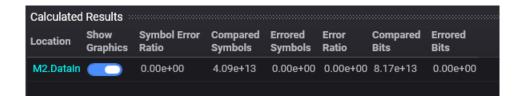

Calculated Results Pane 674

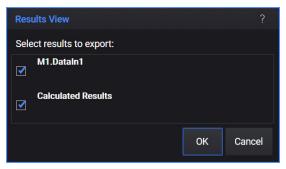

Exporting Measurement Results 675

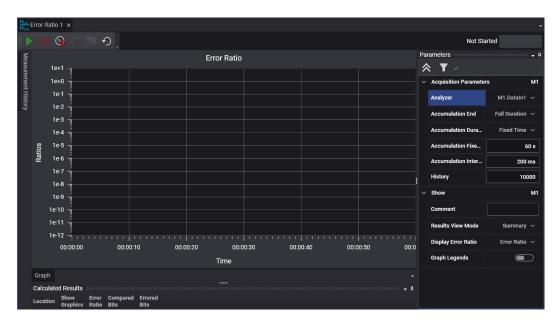

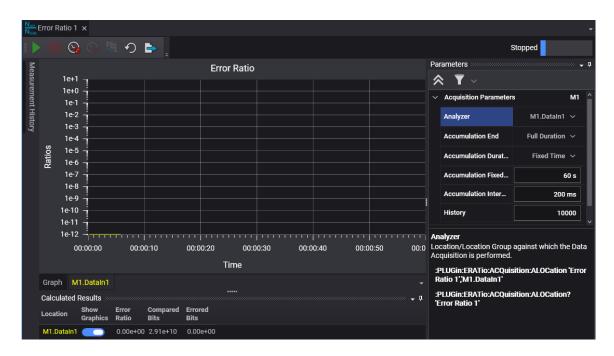

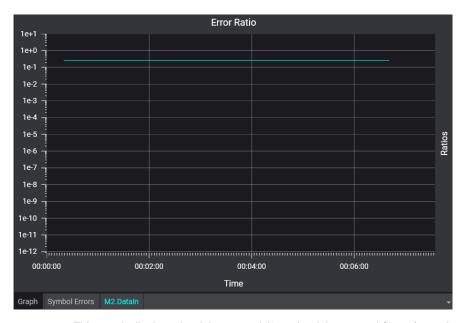

## **Error Ratio Measurement** 676

Overview 676

Launching Error Ratio Measurement 676

Acquisition and Evaluation Parameters for Error Ratio 678

How to Run a Measurement 679

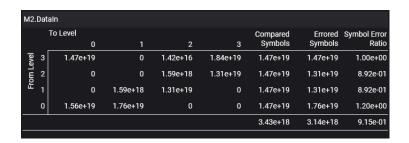

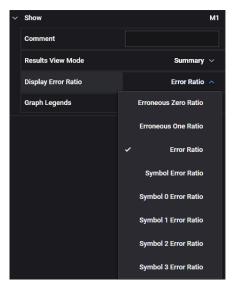

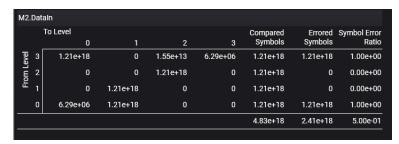

Error Ratio Measurement with PAM4 Symbols 680

How to Stop a Measurement 681

Measurement Graph 682

Test Times and Confidence Levels 683

PAM4 symbol error counters 683

Calculated Results 685

Error Ratio Measurement for a Group of Analyzers 688

#### 9 Utilities

Overview 692

SCPI Recorder 693

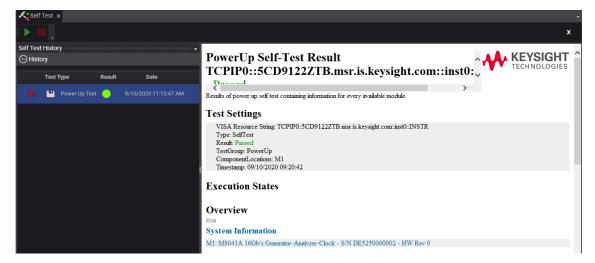

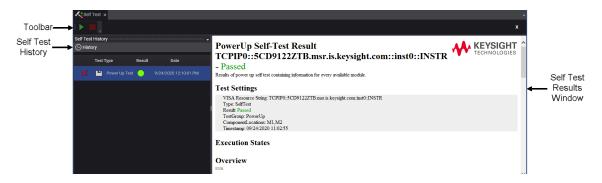

**Self Test Utility** 696

Launching the Self Test Utility 696

Toolbar 697

Self Test History 697

Self Test Results Window 698

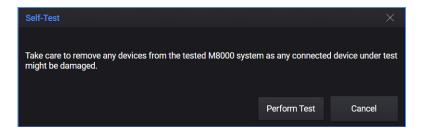

Executing Self Test 698

Aborting Self Test 699

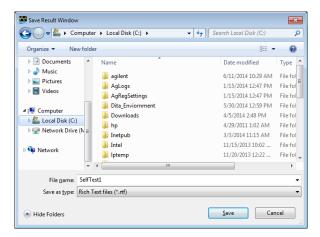

Saving Self Test Results 699

Deleting Self Test Results 700

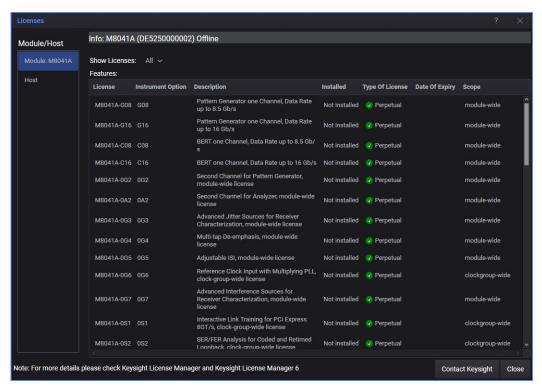

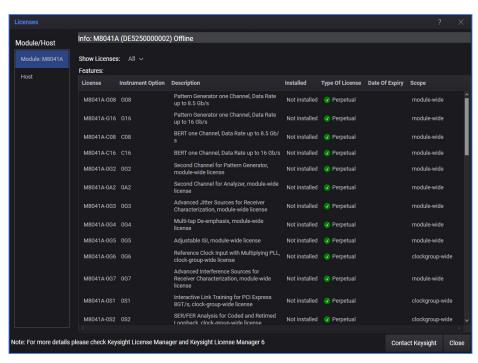

Licenses Window 701

Launching the Licenses Window 701

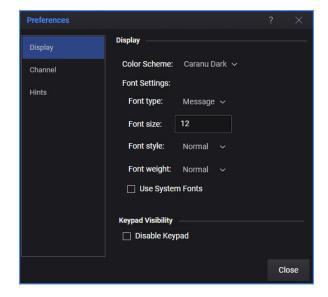

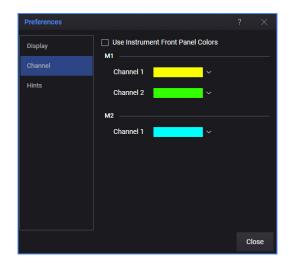

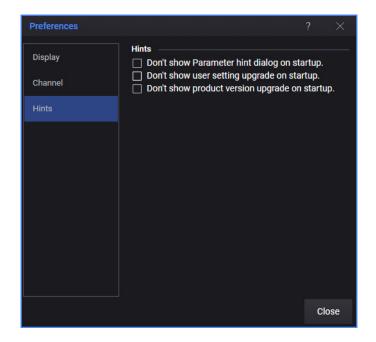

Preferences Window 702

Display Tab 703

Channel Tab 703

Hints Tab 704

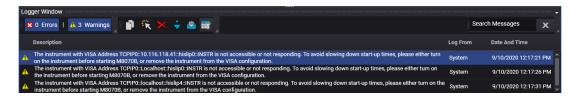

Logger Window 705

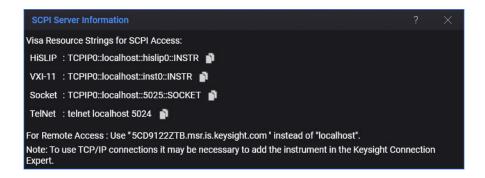

**SCPI Server Information** 706

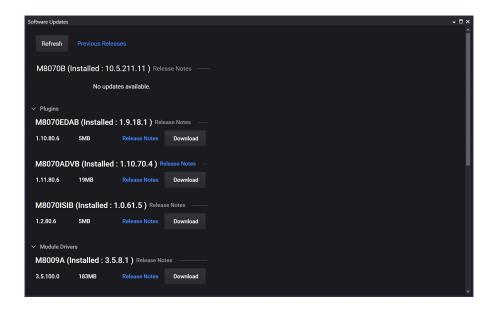

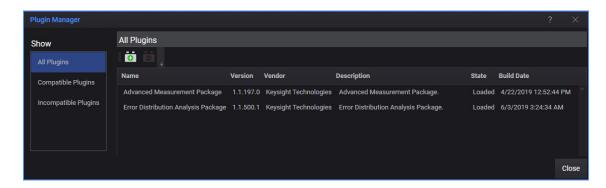

Manage Plug-ins 707

How to Launch Plug-in Manager 707

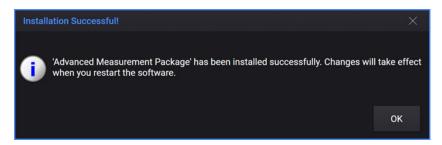

How to Install a Plug-in 709

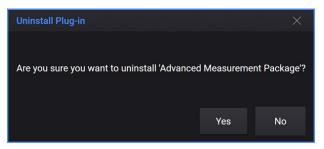

How to Uninstall a Plug-in 710

How to Update a Plug-in 711

How to Access an Installed Plug-in Through M8070B User

Interface 713

#### Manage Instrument Drivers 714

How to launch Manage Instrument Drivers window 714

Instrument Driver States 715

Installing Instrument Drivers in the M8070B System Software 716

Installing/Updating PCI-Express and USB Driver 717

How to Install a Instrument Driver 717

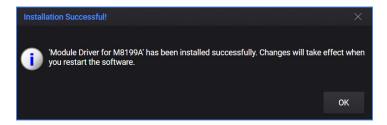

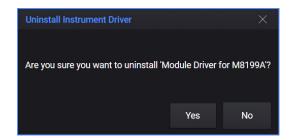

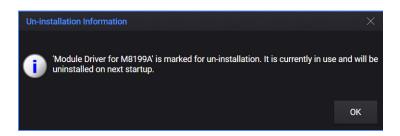

How to Uninstall a Instrument Driver 718

How to Update a Instrument Driver 719

How to Access an Installed Instrument Driver through M8070B User

Interface 721

#### 10 Licenses

#### Overview 724

# License Types 725

Module-Specific Licenses 726

#### **M8020A Licenses** 727

M8041A - High-Performance BERT Module 727

M8041A - License Upgrades for M8041A High-Performance BERT

Module 728

M8051A - High-Performance BERT Module 729

M8051A - License Upgrades for M8051A High-Performance BERT

Module 730

M8062A 32Gb/s Front-end for J-BERT M8020A High-Performance

BERT 731

#### **M8040A Licenses** 733

M8045A Pattern generator and clock module, 32/64 GBd 733 M8046A Analyzer Module, 32/64 GBd 734

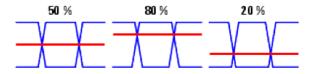

#### **M8050A Licenses** 736

M8042A Pattern Generator Module 736 M8043A Error Analyzer Module 737 M8009A Clock Module 738

#### M8070B Plugin Licenses 739

Advanced Measurement Package Licenses 739

Error Distribution Analysis Package Licenses 740

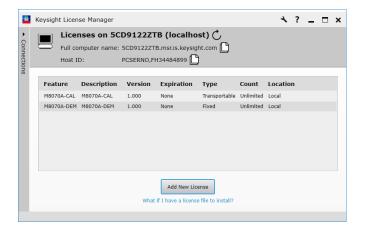

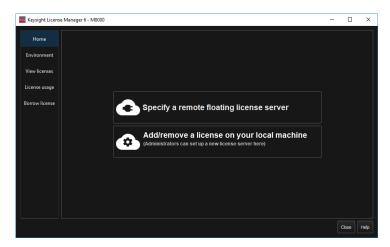

#### Keysight License Manager 742

Keysight License Manager 6 743 Keysight License Manager 5 744

#### **Installing the Licenses** 745

Adding License using Keysight License Manager 6 745

Adding License using Keysight License Manager 5 747

Installing Temporary License (Trial License) 747

Installing Module Licenses (not required for M8020A-BU1, M8040A-BU1 and M8050A-BU1) 748

# 11 Appendix

## **Basic Troubleshooting** 750

Updating software components 750

The chassis does not power up 750

Module is exceptionally hot 750

Contacting Keysight Technologies 750

# **M8070B Factory Patterns** 751

Index

# M8000 Series of BER Test Solutions User Guide

# 1 Introduction

M8020A High-Performance BERT / 28

M8040A High-Performance BERT / 29

M8050A High-Performance BERT 120 GBd / 31

Document History / 33

Related Documents / 34

Abbreviations used in this Document / 35

#### Overview

#### M8020A High-Performance BERT

The Keysight J-BERT M8020A high-performance BERT enables fast, accurate receiver characterization of single-and multi-lane devices running up to 16 or 32 Gb/s.

With today's highest level of integration, the M8020A streamlines your test setup. In addition, automated in situ calibration of signal conditions ensures accurate and repeatable measurements.

Figure 1 Typical base M8020A instrument configuration

#### **Key Features**

- Data rates up to 8.5 and 16 Gb/s expandable to 32 Gb/s

- 1 to 4 BERT channels in a 5-slot AXIe chassis

- Integrated and calibrated jitter injection: RJ, PJ1, PJ2, SJ, BUJ, sinusoidal level interference (common-mode and differential-mode), SSC (triangular and arbitrary, residual) and Clock/2

- · 8 tap deemphasis, positive and negative

- Integrated and adjustable Intersymbol Interference

- Interactive link training for PCI Express

- Built-in clock recovery and equalization

- · All options and modules are upgradeable

#### M8020A Applications

The J-BERT M8020A is designed for R&D and test engineers who characterize and verify compliance of chips, devices, boards and systems with serial I/O ports up to 16 Gb/s and 32 Gb/s in the consumer, computer, mobile computing, data center and communications industry.

The J-BERT M8020A can be used to test popular serial bus standards, such as PCI Express<sup>®</sup>, SATA/SAS, DisplayPort, USB Super Speed, MIPI M-PHY, SD UHS-II, Fibre Channel, QPI, memory buses, backplanes, repeaters, active optical cables, Thunderbolt, 10/40 GbE/SFP+/QSFP, 100 GbE/CFP2.

#### M8040A High-Performance BERT

The Keysight Technologies M8040A is a highly integrated BERT for physical layer characterization and compliance testing.

With support for pulse amplitude modulation 4-level (PAM4) and non-return-to-zero (NRZ) signals, and symbol rates up to 64 GBd (corresponds to 112 Gbit/s) it covers all flavors of the emerging 400 GbE and CEI-56G standards.

The M8040A BERT's true error analysis provides repeatable and accurate results, optimizing the performance margins of your devices.

#### **Key Features**

The M8040A provides the following features:

- · Data rates from 2 to 32 and 64 GBd

- PAM4 and NRZ selectable from M8070B user interface

- Built-in 5 tap deemphasis to compensate loss

- Integrated and calibrated jitter injection: RJ, PJ1, PJ2, SJ, BUJ, and Clk/2 Jitter

- Two pattern generator channels per module to emulate aggressor

- Linearity tests with adjustable PAM4 levels

- Short connections to the DUT with remote heads for the pattern generator

- True PAM4 error detection in real-time for low BER levels

- Graphical user interface and remote control via M8000 system software

- · Scalable and upgradeable with options and modules

- Clock recovery with N1076A and N1077A

#### M8040A Applications

The M8040A is designed for R&D and test engineers who characterize chips, devices, transceiver modules and sub-components, boards and systems with serial I/O ports operating with data rates up to 32 GBd and 64 GBd in the data center and communications industries.

The M8040A can be used for receiver (input) testing for many popular interconnect standards, such as:

- 400 Gigabit Ethernet (IEEE 802.3bs)

- 200/100/50 Gigabit Ethernet

- OIF CEI 56G (NRZ and PAM4 versions)

- 64G/112G Fibre Channel

- Infiniband-HDR

- · CDAUI-8

- Proprietary interfaces for chip-to-chip, chip-to-module, backplanes, repeaters, and active optical cables, operating up to 64 GBd.

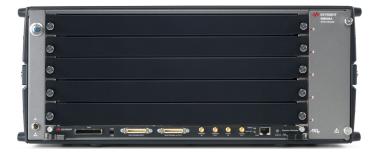

Figure 2 Typical M8040A instrument configuration

#### M8050A High-Performance BERT 120 GBd

The Keysight M8050A high-performance bit error ratio tester (BERT) enables accurate characterization of receivers used in next-generation data center networks and server interfaces. With uncompromised signal integrity, support for NRZ, PAM4, PAM6, and PAM8 signals, and data rates up to 120 GBd, the flexible architecture of the M8050A supports 1.6T path finding as well as other leading-edge technologies.

The M8050A high-performance BERT is one part of the Keysight M8000 Series of BER test solutions. It can be combined with other hardware and software of the M8000 Series.

The M8050A is a modular instrument which supports the following modules:

- M8042A Pattern Generator Module

- M8043A Error Analyzer Module

- M8009A Clock Module

- M8058A/M8059A Remote Head for M8042A Pattern Generator

- M8052A Remote Head for M8043A Error Analyzer

M8050A being a modular product includes different sets of modules which are hosted in an AXI chassis. Each module and its features have their own license. You need to install these options in your instrument in order to use the modules or features. For details, refer to the chapter Licenses on page 723. However, if you have ordered M8050A-BU2/BU3/BU4/BU5, no license is required.

For details on the features and hardware components of each of the above mentioned modules, refer to M8050A Getting Started Guide.

#### **Key Features**

- M8042A Pattern Generator:

- Symbol rates from 2 to 120 GBd

- Line coding: NRZ, PAM3, PAM4, PAM6, and PAM8

- Built-in seven tap de-emphasis for improved channel loss compensation

- Transition time at < 5 ps and < 100 fs root mean square (RMS) intrinsic random jitter

- Jitter injection integrated and calibrated for receiver tolerance testing RJ, PJ1, PJ2, BUJ, sRJ, and clk / 2

- M8043A Error Analyzer Module:

- Symbol rates from 2 to 64.4 GBd

- Line coding: NRZ, and PAM4

- Built-in 16-tap FFE for improved channel loss compensation

- Built-in CTLE and 256-tap FIR filter improved channel loss compensation

- Flexible solution with software license upgradeable functionality

#### M8050A Applications

The M8050A helps engineers design and characterize chips, devices, transceiver modules, sub-components, boards, and systems. Quickly test serial I/O ports operating at data rates up to 120 GBd across the server, computing, data center, and communication industries. Combining the M8050A BERT with a Keysight UXR-Series 80 GHz oscilloscope gives you a full 1.6T receiver and transmitter test solution to assess your Ethernet systems.

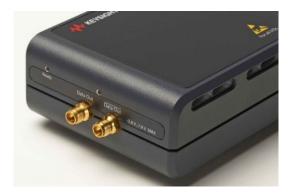

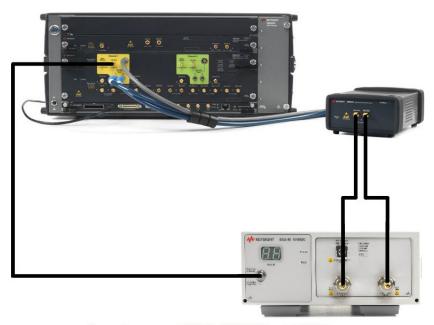

Figure 3 Typical M8050A instrument configuration

# Document History

Table 3 Document History

| Edition                     | Description                                                                                                         |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------|

| Edition 1.0, December 2018  | Edition 1.0 of the M8000 Series User Guide is in accordance to the M8070B version 6.0.                              |

| Edition 2.0, May 2019       | Edition 2.0 of the M8000 Series User Guide is in accordance to the M8070B version 6.5.                              |

| Edition 3.0, October 2019   | Edition 3.0 of the M8000 Series User Guide is in accordance to the M8070B version 6.7.                              |

| Edition 3.3, April 2020     | Edition 3.3 of the M8000 Series User Guide is in accordance to the M8070B version 7.0.                              |

| Edition 3.6, June 2020      | Edition 3.6 of the M8000 Series User Guide is in accordance to the M8070B version 7.1.                              |

| Edition 3.7, July 2020      | Edition 3.7 of the M8000 Series User Guide is in accordance to the M8070B version 7.2.                              |

| Edition 4.1, February 2021  | Edition 4.1 of the M8000 Series User Guide is in accordance to the M8070B version 7.5.                              |

| Edition 5.0, April 2021     | Edition 5.0 of the M8000 Series User Guide is in accordance to the M8070B version 8.0.                              |

| Edition 6.0, November 2021  | Edition 6.0 of the M8000 Series User Guide is in accordance to the M8070B version 8.5.                              |

| Edition 7.0, April 2022     | Edition 7.0 of the M8000 Series User Guide is in accordance to the M8070B version 9.0 and M8042A initial release.   |

| Edition 8.0, July 2022      | Edition 8.0 of the M8000 Series User Guide is in accordance to the M8070B version 9.1.                              |

| Edition 9.0, October 2022   | Edition 9.0 of the M8000 Series User Guide is in accordance to the M8070B version 9.5.                              |

| Edition 10.0, December 2022 | Edition 10.0 of the M8000 Series User Guide is in accordance to the M8070B version 9.5.1.                           |

| Edition 11.0, April 2023    | Edition 11.0 of the M8000 Series User Guide is in accordance to the M8070B version 10.0.                            |

| Edition 12.0, July 2023     | Edition 12.0 of the M8000 Series User Guide is in accordance to the M8070B version 10.1 and M8043A initial release. |

| Edition                     | Description                                                                                                                 |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Edition 13.0, November 2023 | Edition 13.0 of the M8000 Series User Guide is in accordance to the M8070B version 10.5, M8042A 3.5 and M8043A 3.5 release. |

| Edition 14.0, April 2024    | Edition 14.0 of the M8000 Series User Guide is in accordance to the M8070B version 11.0.                                    |

# Related Documents

Table 4 Related Documents

| Document Part No. | Document Title                                               |

|-------------------|--------------------------------------------------------------|

| M8000-91B01       | M8020A Start Here                                            |

| M8000-91B03       | M8040A Start Here                                            |

| M8000-91B20       | M8050A Start Here                                            |

| M8000-91B04       | M8000 Series Tips for Preventing Damage                      |

| M8000-91B05       | M8000 Series Installation Guide                              |

| M8000-91B06       | M8020A Getting Started Guide                                 |

| M8000-91B07       | M8040A Getting Started Guide                                 |

| M8000-91B21       | M8050A Getting Started Guide                                 |

| M8000-91B08       | M8000 Series BER Test Solutions User Guide                   |

| M8000-91B09       | M8000 Series BER Test Solutions Programming Guide            |

| M8000-91B14       | M8000 Series Plugins Getting Started Guide                   |

| M8000-91B10       | M8000 Series Advance Measurement Package User Guide          |

| M8000-91B11       | M8000 Series Error Distribution Analysis Package User Guide  |

| M8000-91B15       | M8070ISIB Adjustable ISI Package for M8000 Series User Guide |

# Abbreviations used in this Document

Table 5 Abbreviations

| AXIe AdvancedTCA Extensions for Instrumentation and Test AWG Arbitrary Waveform Generator  BER Bit Error Ratio  CDR Clock Data Recovery  CTLE Continuous-Time Linear Equalizer  DUT Device Under Test  ESD Electrostatic Discharge  ESM Embedded System Module  GB Gigabyte  GUI Graphical User Interface  J-BERT Jitter-Bit Error Ratio Tester  LED Light-Emitting Diode  MB Megabyte  MIPI Mobile Industry Processor Interface  PC Personal Computer  PCIe Peripheral Component Interconnect Express  PLL Phase Locked Loop  PRBS Pseudorandom Binary Sequence  PXI PCI extensions for Instrumentation  R & D Research & Development  SAS Serial Advanced Technology Attachment  SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A  SSC Spread Spectrum Clock | Abbreviation | Extended Form                                       |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------|--|

| BER Bit Error Ratio  CDR Clock Data Recovery  CTLE Continuous-Time Linear Equalizer  DUT Device Under Test  ESD Electrostatic Discharge  ESM Embedded System Module  GB Gigabyte  GUI Graphical User Interface  J-BERT Jitter-Bit Error Ratio Tester  LED Light-Emitting Diode  MB Megabyte  MIPI Mobile Industry Processor Interface  PC Personal Computer  PCle Peripheral Component Interconnect Express  PLL Phase Locked Loop  PRBS Pseudorandom Binary Sequence  PXI PCI eXtensions for Instrumentation  R & D Research & Development  SAS Serial Attached SCSI  SATA Serial Advanced Technology Attachment  SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A                                                                                            | AXIe         | AdvancedTCA Extensions for Instrumentation and Test |  |

| CDR Clock Data Recovery  CTLE Continuous-Time Linear Equalizer  DUT Device Under Test  ESD Electrostatic Discharge  ESM Embedded System Module  GB Gigabyte  GUI Graphical User Interface  J-BERT Jitter-Bit Error Ratio Tester  LED Light-Emitting Diode  MB Megabyte  MIPI Mobile Industry Processor Interface  PC Personal Computer  PCIe Peripheral Component Interconnect Express  PLL Phase Locked Loop  PRBS Pseudorandom Binary Sequence  PXI PCI extensions for Instrumentation  R & D Research & Development  SAS Serial Attached SCSI  SATA Serial Advanced Technology Attachment  SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A                                                                                                                 | AWG          | Arbitrary Waveform Generator                        |  |

| CTLE Continuous-Time Linear Equalizer  DUT Device Under Test  ESD Electrostatic Discharge  ESM Embedded System Module  GB Gigabyte  GUI Graphical User Interface  J-BERT Jitter-Bit Error Ratio Tester  LED Light-Emitting Diode  MB Megabyte  MIPI Mobile Industry Processor Interface  PC Personal Computer  PCle Peripheral Component Interconnect Express  PLL Phase Locked Loop  PRBS Pseudorandom Binary Sequence  PXI PCI eXtensions for Instrumentation  R & D Research & Development  SAS Serial Attached SCSI  SATA Serial Advanced Technology Attachment  SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A                                                                                                                                          | BER          | Bit Error Ratio                                     |  |

| DUT Device Under Test  ESD Electrostatic Discharge  ESM Embedded System Module  GB Gigabyte  GUI Graphical User Interface  J-BERT Jitter-Bit Error Ratio Tester  LED Light-Emitting Diode  MB Megabyte  MIPI Mobile Industry Processor Interface  PC Personal Computer  PCIe Peripheral Component Interconnect Express  PLL Phase Locked Loop  PRBS Pseudorandom Binary Sequence  PXI PCI eXtensions for Instrumentation  R & D Research & Development  SAS Serial Attached SCSI  SATA Serial Advanced Technology Attachment  SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A                                                                                                                                                                                 | CDR          | Clock Data Recovery                                 |  |

| ESD Electrostatic Discharge  ESM Embedded System Module  GB Gigabyte  GUI Graphical User Interface  J-BERT Jitter-Bit Error Ratio Tester  LED Light-Emitting Diode  MB Megabyte  MIPI Mobile Industry Processor Interface  PC Personal Computer  PCIe Peripheral Component Interconnect Express  PLL Phase Locked Loop  PRBS Pseudorandom Binary Sequence  PXI PCI eXtensions for Instrumentation  R & D Research & Development  SAS Serial Attached SCSI  SATA Serial Advanced Technology Attachment  SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A                                                                                                                                                                                                        | CTLE         | Continuous-Time Linear Equalizer                    |  |

| ESM Embedded System Module  GB Gigabyte  GUI Graphical User Interface  J-BERT Jitter-Bit Error Ratio Tester  LED Light-Emitting Diode  MB Megabyte  MIPI Mobile Industry Processor Interface  PC Personal Computer  PCIe Peripheral Component Interconnect Express  PLL Phase Locked Loop  PRBS Pseudorandom Binary Sequence  PXI PCI eXtensions for Instrumentation  R & D Research & Development  SAS Serial Attached SCSI  SATA Serial Advanced Technology Attachment  SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A                                                                                                                                                                                                                                     | DUT          | Device Under Test                                   |  |

| GB Gigabyte  GUI Graphical User Interface  J-BERT Jitter-Bit Error Ratio Tester  LED Light-Emitting Diode  MB Megabyte  MIPI Mobile Industry Processor Interface  PC Personal Computer  PCIe Peripheral Component Interconnect Express  PLL Phase Locked Loop  PRBS Pseudorandom Binary Sequence  PXI PCI eXtensions for Instrumentation  R & D Research & Development  SAS Serial Attached SCSI  SATA Serial Advanced Technology Attachment  SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A                                                                                                                                                                                                                                                                 | ESD          | Electrostatic Discharge                             |  |

| GUI Graphical User Interface  J-BERT Jitter-Bit Error Ratio Tester  LED Light-Emitting Diode  MB Megabyte  MIPI Mobile Industry Processor Interface  PC Personal Computer  PCIe Peripheral Component Interconnect Express  PLL Phase Locked Loop  PRBS Pseudorandom Binary Sequence  PXI PCI eXtensions for Instrumentation  R & D Research & Development  SAS Serial Attached SCSI  SATA Serial Advanced Technology Attachment  SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A                                                                                                                                                                                                                                                                              | ESM          | Embedded System Module                              |  |

| J-BERT Jitter-Bit Error Ratio Tester  LED Light-Emitting Diode  MB Megabyte  MIPI Mobile Industry Processor Interface  PC Personal Computer  PCIe Peripheral Component Interconnect Express  PLL Phase Locked Loop  PRBS Pseudorandom Binary Sequence  PXI PCI eXtensions for Instrumentation  R & D Research & Development  SAS Serial Attached SCSI  SATA Serial Advanced Technology Attachment  SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A                                                                                                                                                                                                                                                                                                            | GB           | Gigabyte                                            |  |

| LED Light-Emitting Diode  MB Megabyte  MIPI Mobile Industry Processor Interface  PC Personal Computer  PCle Peripheral Component Interconnect Express  PLL Phase Locked Loop  PRBS Pseudorandom Binary Sequence  PXI PCI eXtensions for Instrumentation  R & D Research & Development  SAS Serial Attached SCSI  SATA Serial Advanced Technology Attachment  SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A                                                                                                                                                                                                                                                                                                                                                  | GUI          | Graphical User Interface                            |  |

| MIPI Mobile Industry Processor Interface  PC Personal Computer  PCIe Peripheral Component Interconnect Express  PLL Phase Locked Loop  PRBS Pseudorandom Binary Sequence  PXI PCI eXtensions for Instrumentation  R & D Research & Development  SAS Serial Attached SCSI  SATA Serial Advanced Technology Attachment  SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A                                                                                                                                                                                                                                                                                                                                                                                         | J-BERT       | Jitter-Bit Error Ratio Tester                       |  |

| MIPI Mobile Industry Processor Interface  PC Personal Computer  PCIe Peripheral Component Interconnect Express  PLL Phase Locked Loop  PRBS Pseudorandom Binary Sequence  PXI PCI eXtensions for Instrumentation  R & D Research & Development  SAS Serial Attached SCSI  SATA Serial Advanced Technology Attachment  SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A                                                                                                                                                                                                                                                                                                                                                                                         | LED          | Light-Emitting Diode                                |  |

| PC Personal Computer  PCIe Peripheral Component Interconnect Express  PLL Phase Locked Loop  PRBS Pseudorandom Binary Sequence  PXI PCI eXtensions for Instrumentation  R & D Research & Development  SAS Serial Attached SCSI  SATA Serial Advanced Technology Attachment  SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A                                                                                                                                                                                                                                                                                                                                                                                                                                   | МВ           | Megabyte                                            |  |

| PCIe Peripheral Component Interconnect Express  PLL Phase Locked Loop  PRBS Pseudorandom Binary Sequence  PXI PCI eXtensions for Instrumentation  R & D Research & Development  SAS Serial Attached SCSI  SATA Serial Advanced Technology Attachment  SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MIPI         | Mobile Industry Processor Interface                 |  |

| PLL Phase Locked Loop  PRBS Pseudorandom Binary Sequence  PXI PCI eXtensions for Instrumentation  R & D Research & Development  SAS Serial Attached SCSI  SATA Serial Advanced Technology Attachment  SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PC           | Personal Computer                                   |  |

| PRBS Pseudorandom Binary Sequence  PXI PCI eXtensions for Instrumentation  R & D Research & Development  SAS Serial Attached SCSI  SATA Serial Advanced Technology Attachment  SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PCle         | Peripheral Component Interconnect Express           |  |

| PXI PCI eXtensions for Instrumentation  R & D Research & Development  SAS Serial Attached SCSI  SATA Serial Advanced Technology Attachment  SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PLL          | Phase Locked Loop                                   |  |

| R & D Research & Development  SAS Serial Attached SCSI  SATA Serial Advanced Technology Attachment  SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PRBS         | Pseudorandom Binary Sequence                        |  |

| SAS Serial Attached SCSI  SATA Serial Advanced Technology Attachment  SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PXI          | PCI eXtensions for Instrumentation                  |  |

| SATA Serial Advanced Technology Attachment  SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R & D        | Research & Development                              |  |

| SCPI Standard Commands for Programmable Instruments  SMA SubMiniature Version A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SAS          | Serial Attached SCSI                                |  |

| SMA SubMiniature Version A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SATA         | Serial Advanced Technology Attachment               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SCPI         | Standard Commands for Programmable Instruments      |  |

| SSC Spread Spectrum Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SMA          | SubMiniature Version A                              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SSC          | Spread Spectrum Clock                               |  |

| Abbreviation | Extended Form                 |

|--------------|-------------------------------|

| TCP          | Transmission Control Protocol |

| USB          | Universal Serial Bus          |

| VCO          | Voltage Controlled Oscillator |

# M8000 Series of BER Test Solutions User Guide

## 2 Know Your Hardware

M8020A Overview / 38 M9505A AXIe Chassis / 39 M9506A AXIe Chassis / 40 Host Computer / 43 M8020A Modules / 45 M8020A Module Setup / 57 M8040A Overview / 59 M8040A Overview / 59 M8040A Modules / 60 M8040A Module Setup / 69 M8050A Overview / 70 M8050A Modules / 71 M8050A Module Setup / 84 M8070B Supported Plugins / 86 M8100 Series Arbitrary Waveform Generators / 87 M8054A Interference Source Module / 93 M8047A PCI Express Re-driver / 94 M8047B PCI Express Re-driver / 95 Other Supported Hardware(s) / 96 Hardware Setup for M8046A and M8062A Modules / 104 ESD Protection / 106

#### M8020A Overview

The Keysight's J-BERT M8020A High-Performance BERT is a modular instrument which supports the following modules:

- M8041A high-performance BERT generator-analyzer-clock 8/16 Gb/s

- M8051A high-performance BERT generator-analyzer 8/16 Gb/s.

- M8062A 32Gb/s Front-end for J-BERT M8020A High-Performance BERT

- In addition to above J-BERT modules, it also supports M8194A, M8195A, and M8196A Arbitrary Waveform Generator modules. Details of these modules can be found at

- www.keysight.com/find/M8194A

- www.keysight.com/find/M8195A

- www.keysight.com/find/M8196A

M8020A being a modular product includes different sets of modules which are hosted in an AXI chassis. Each module and its features have their own license. You need to install these options in your instrument in order to use the modules or features. For details, refer to the chapter Licenses on page 723. However, if you have ordered M8020A-BU1, no license is required.

The M8041A module must be installed in slots 1 through 3 in the AXIe chassis unless the M9536A AXIe Embedded Controller is installed. The following configurations are possible in an M9505A 5-slot chassis:

- 1 or 2-channel, 16 Gb/s (1) M8041A

- 3 or 4-channel, 16 Gb/s (1) M8041A + (1) M8051A

- 1-channel, 32 Gb/s (Pattern Generator only or full BERT) (1)

M8041A + (1) M8062A

- M8194A/M8195A/M8196A module can be added into the 5 slot module

Additionally, the M8062A and M8194A/M8195A/M8196A modules can be installed and operated in a 2 slot frame.

#### NOTE

In case an AWG module (M8194A/M8195A/M8196A) is used in a combined system with M8020A modules, ensure that the AWG modules are mounted in a slot number higher than M8020A modules in the AXIe chassis. In other words, an AWG module always has to be mounted last in the chassis.

For details on the features and hardware components of each of the above-mentioned modules, refer to M8020A Modules on page 45.

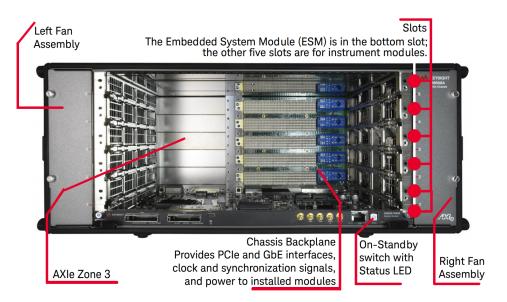

#### M9505A AXIe Chassis

The M9505A AXIe Chassis is a modular instrument chassis that supports complex and high density testing. The chassis provides slots for installing multiple AXIe based instrument modules such as the M8041A, M8042A, M8043A, M8045A, M8046A, M8051A, M8062A and M8009A modules. Besides providing a frame for the installation of these instrument modules, the M9505A AXIe Chassis also provides power, a cooling system, a PCIe Gen2 local data bus, a Gigabit LAN interconnect, and a cabled USB (USB option required) and PCIe connection for external host computer connectivity.

The following model of the M9505A AXIe Chassis supports the M8020A modules:

M9505A - a 5-Slot AXIe chassis

NOTE

The USB connection is recommended when using a laptop or desktop PC as an external controller. The PCIe connection is recommended for use with a desktop PC as an external controller only.

Refer to the *Keysight M9505A AXIe Chassis Startup Guide* to get detailed information about the AXIe chassis.

#### AXIe Embedded System Module (USB ESM)

The bottom slot of the AXIe chassis is reserved for the Embedded System Module (ESM) which is factory-installed. The ESM has a USB 2.0 interface as well as a PCIe x8, Gen1 and Gen2 compliant interface to connect an external host computer to the chassis. The following figure shows the PCIe Port and USB Port in ESM

#### The ESM:

- runs the chassis embedded operating system which manages all internal tasks and communications.

- tracks inserted modules and manages power requirements.

- monitors chassis temperature and controls variable-speed chassis fans.

- monitors module sensors and reports component failures to a system log.

- acts as a Gigabit Ethernet switch; forwards frames along the backplane.

- · connects an external host computer to the chassis.

- synchronizes timing across all modules through the Keysight Trigger Bus, using an internal or external clock source.

- LAN connector on AXIe ESM is not used. Only use LAN connection on the host computer.

- Either the PCIe (desktop only) or USB (desktop or laptop) port can be used in this ESM but not both simultaneously. When you use the PCIe port, the USB port is automatically disabled until the PCIe port is no longer in use.

#### M9506A AXIe Chassis

The Keysight M9506A AXIe chassis is a modular instrument chassis fully compatible with the AXIe Wide PCIe specification. It allows multiple application-specific instrument modules to share a common chassis frame, power supply, cooling system, PCI Express (PCIe) x16 Generation (Gen) 3 backplane, Gigabit LAN hub, local bus for module-to-module signaling, and host PC connections. The full rack chassis provides five general purpose peripheral slots that accept 1U AXIe instrument modules.

Additional features include:

- · Up to 300 W per slot power

- Five AXIe Wide compliant slots

- PCIe x16 Gen 3 Backplane allows module to module communication

- Default PCIe configuration merges both cable ports to one Gen 3 x16 PCIe Cable Port.

- Open AXIe Zone 3 for custom use (cable access, analog backplane, etc.)

- Thunderbolt™ 3 Connection Port<sup>1</sup>

- · Cascaded PCIe for multiple chassis systems

- Parallel and Star Triggering

- · Push-pull fan system for quieter operation

The chassis includes a half-height Embedded System Module (ESM) that manages chassis functions. The ESM provides all ATCA (Advanced Telecommunications Computing Architecture) shelf manager functions, plus these AXIe extensions:

- Host PC connectivity (Gen 3 PCle x8/x16, Thunderbolt 3, Ethernet)

- Sources timing signals (CLK100, SYNC, and FCLK)

- · Routes STRIG (Star Trigger) to instruments through the backplane

- Two bi-directional trigger access ports route trigger signals through to the backplane parallel trigger bus and star triggers (STRIG) to each slot

- Provides backplane PCIe and Ethernet communication between modules

Other than a power button/status light (on the ESM), all monitoring, control, and communication with the chassis requires a host PC. This can be an embedded PC specifically designed for use in an AXIe chassis (such as the Keysight M9537A) or remote (a rackmount, desktop, or laptop) PC.

The Gen 3 PCIe Cable Interface ports provides up to a 8GB/s (theoretical) for Gen 3 x8 and 16 GB/s (theoretical) for Gen 3 x16. The Thunderbolt 3 port provides a Gen 3 x4 link with up to 4 GB/s (theoretical) bandwidth.

<sup>1</sup> Thunderbolt™ is the brand name of an interface standard developed by Intel (in conjunction with Apple) that allows connection of external peripherals to a computer. Thunderbolt 3 specification provides Gen 3 PCI Express (PCIe), DisplayPort, and DC power in one USB-C compatible cable; only PCIe is supported on the M9506A. Charging devices such as laptop computers over Thunderbolt 3 is not supported on the M9506A.

Refer to the Keysight M9506A 5-Slot AXIe Chassis Startup Guide to get detailed information about the AXIe chassis.

## Host Computer

A host computer is used to:

- host all the software components of the instrument modules needed to control, configure, and use the modules.

- communicate with the ESM of the M9505A AXIe Chassis to allow you to monitor and control the chassis.

A host computer can be:

- the M9537A AXIe Embedded Controller module.

- · a laptop with a USB port or with PCIe port.

- a desktop PC with a USB port or x8 or wider PCle slot for the cabled PCle adapter card.

Keysight M9537A AXIe Embedded Controller Module

The M9537A AXIe Embedded Controller is a one slot module that you can install in the M9505A AXIe Chassis like any other instrument module. This module acts as a host computer when installed in the M9505A AXIe Chassis. It is always installed in slot 1 of the M9505A AXIe Chassis.

The following figure displays this module.

Keysight M9537A AXIe Embedded Controller Module

The M9537A AXIe Embedded Controller is a one slot module that you can install in the M9505A AXIe Chassis like any other instrument module. This module acts as a host computer when installed in the M9505A AXIe Chassis. It is always installed in slot 1 of the M9505A AXIe Chassis. It may be installed in any slot of the M9514A AXIe chassis except for Slot 7 which is reserved for the ASM. However, to eliminate interference with the local

bus used for E-Keying (if your AXIe modules use E-Keying), you should install the controller in one of the outside slots; e.g., 1 or 14 first, then 2 or 13, etc.

The following figure displays this module:

#### The ESM:

- runs the chassis embedded operating system which manages all internal tasks and communications.

- tracks inserted modules and manages power requirements.

- monitors chassis temperature and controls variable- speed chassis fans.

- monitors module sensors and reports component failures to a system log.

- · acts as a Gigabit Ethernet switch; forwards frames along the backplane.

- · connects an external host computer to the chassis.

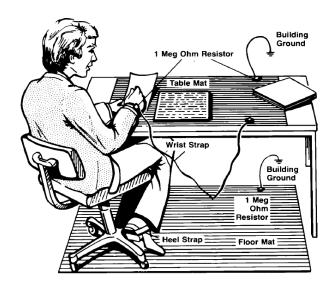

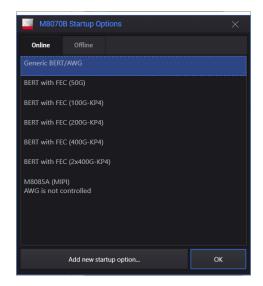

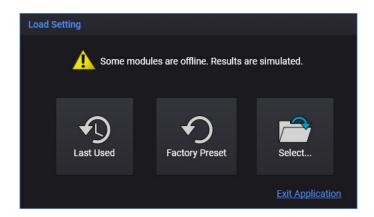

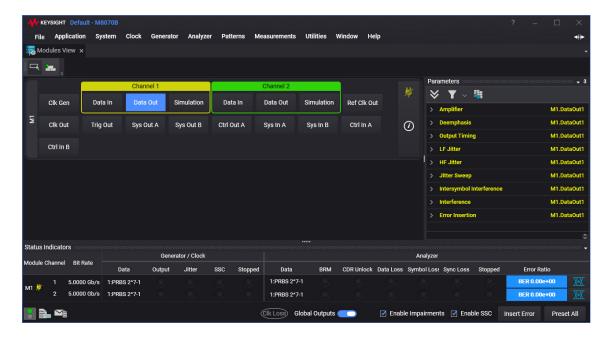

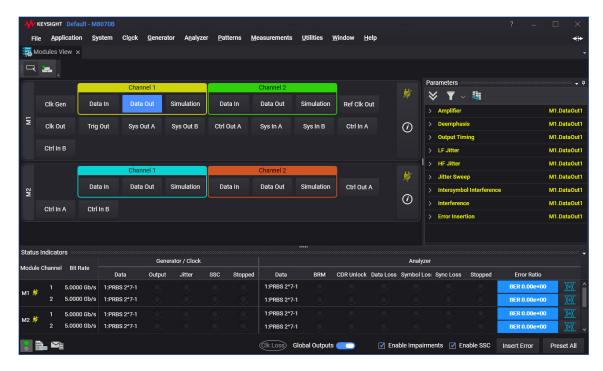

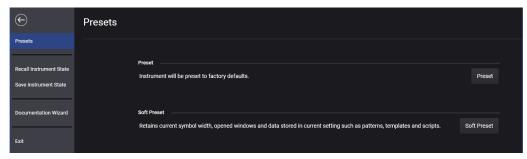

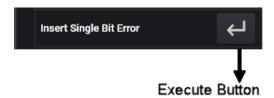

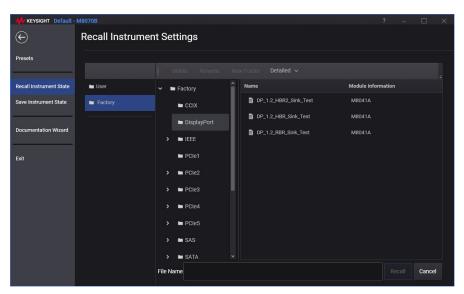

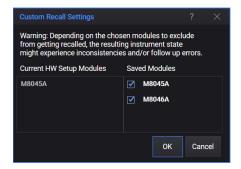

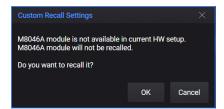

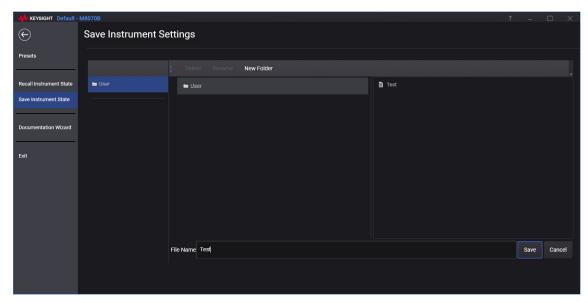

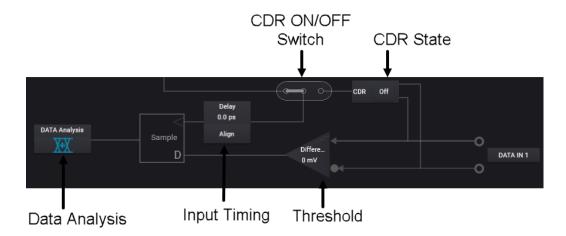

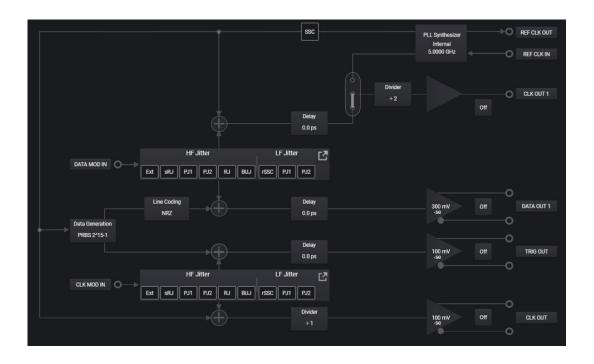

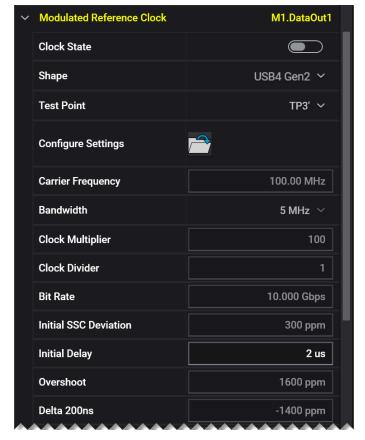

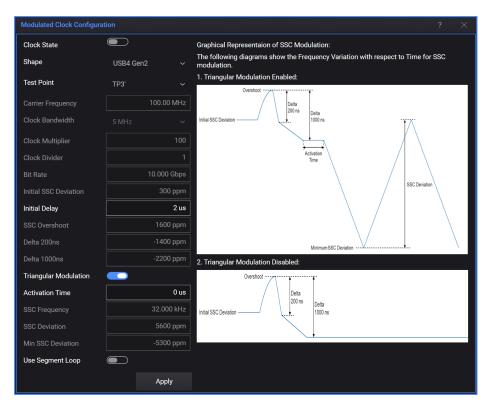

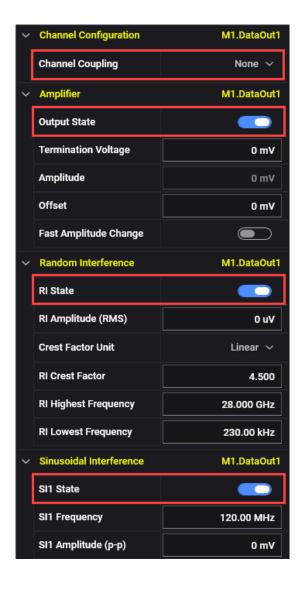

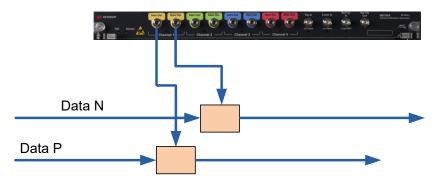

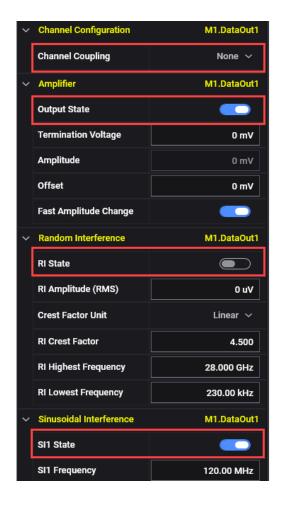

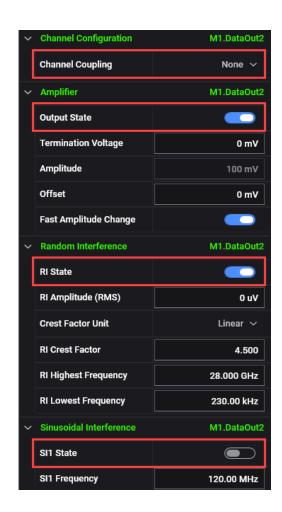

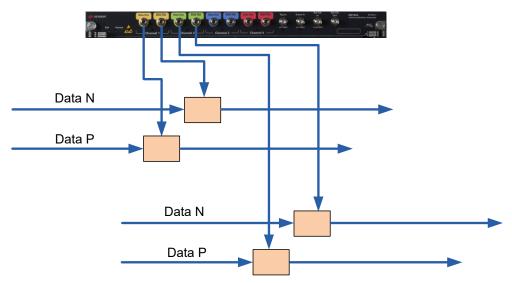

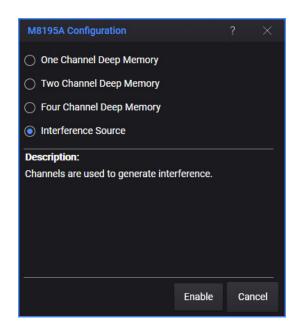

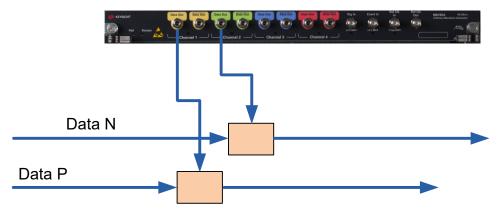

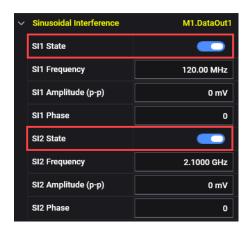

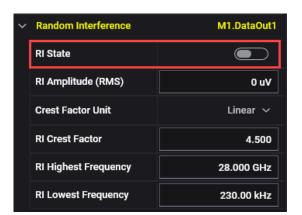

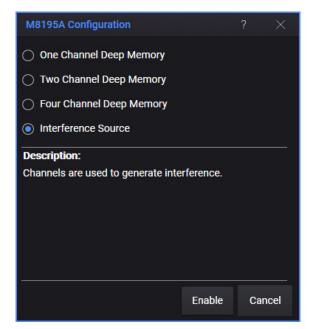

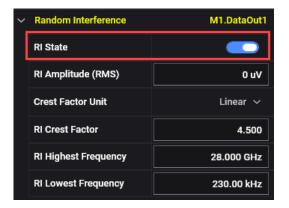

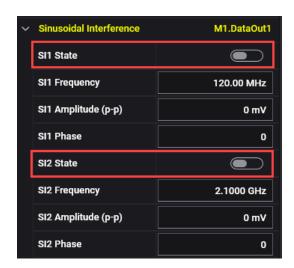

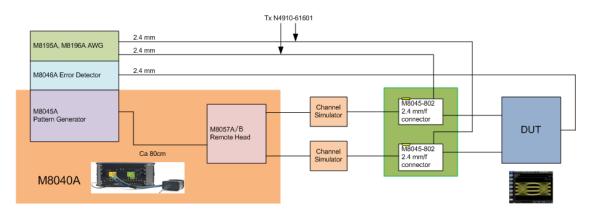

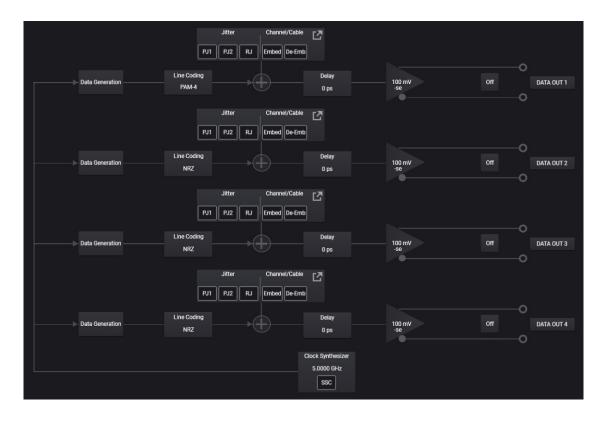

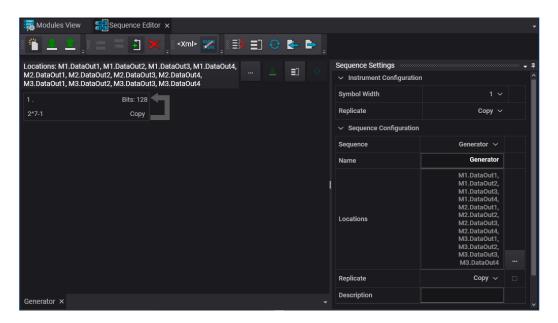

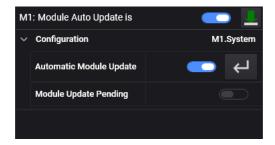

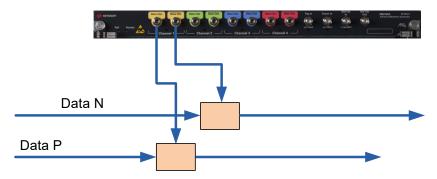

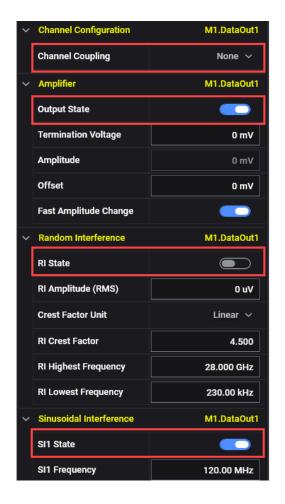

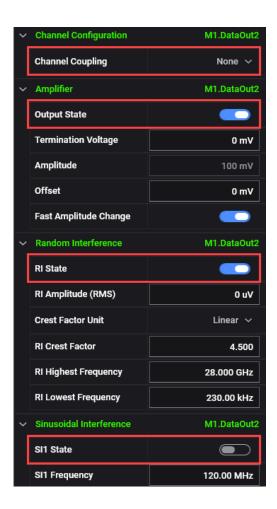

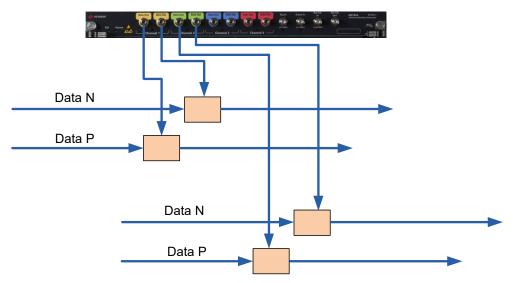

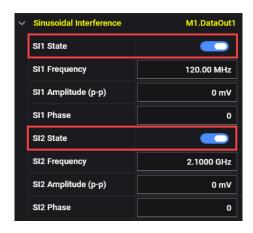

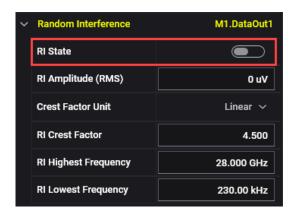

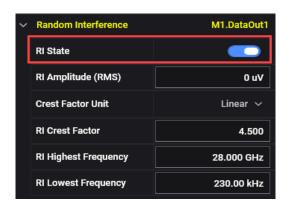

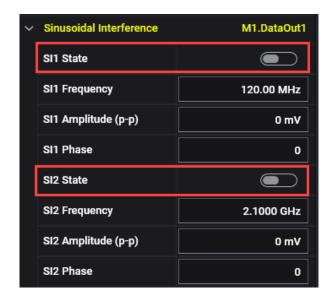

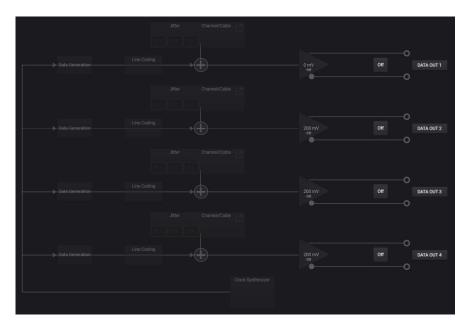

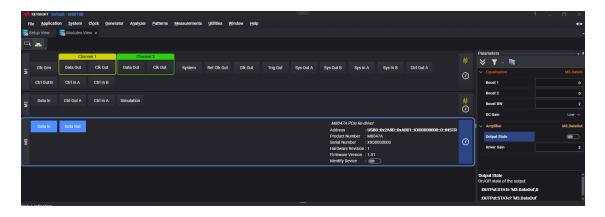

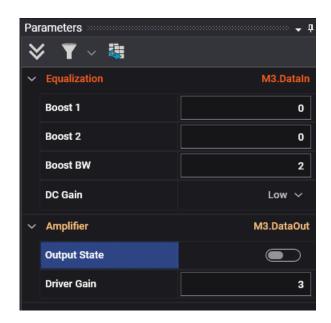

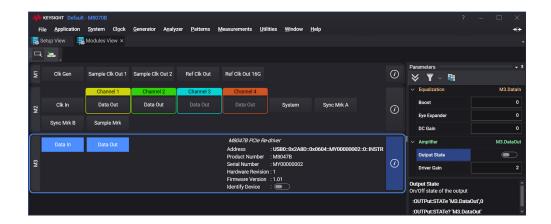

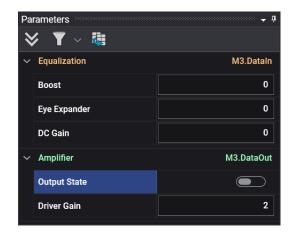

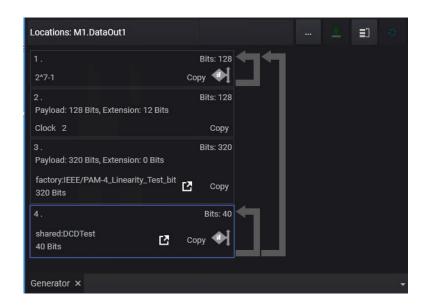

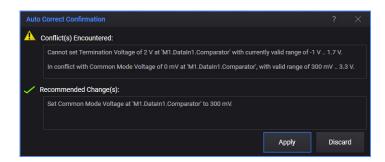

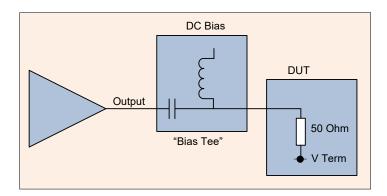

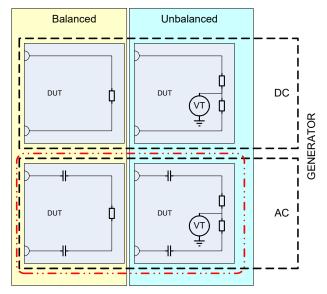

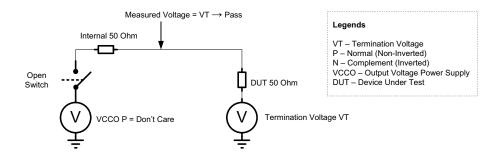

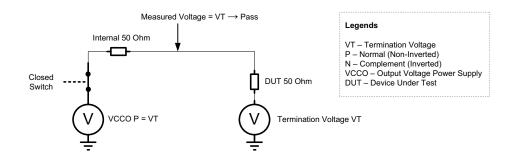

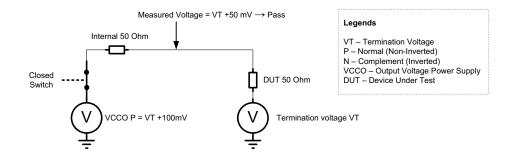

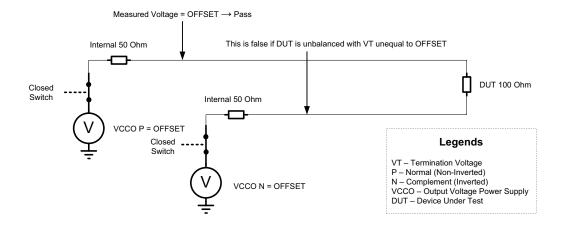

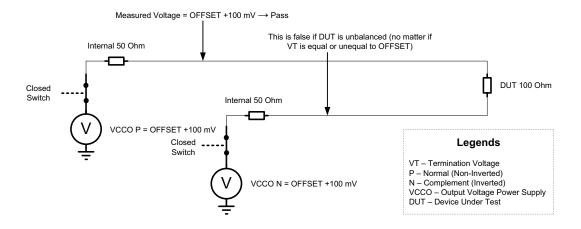

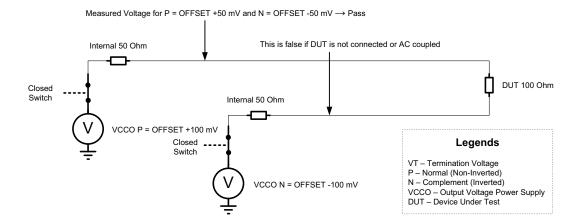

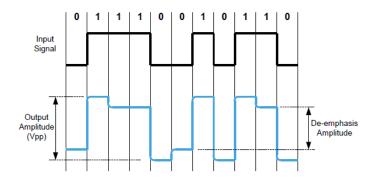

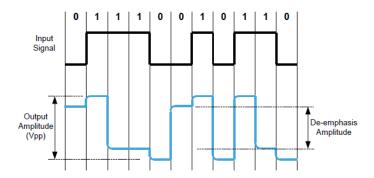

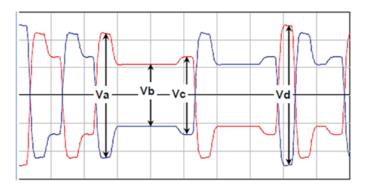

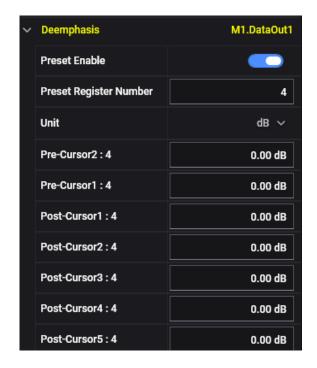

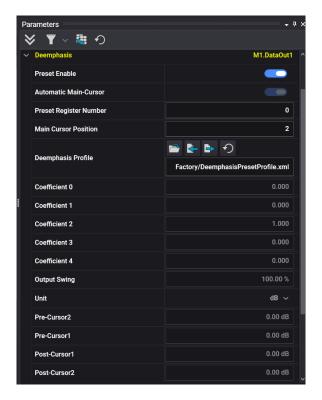

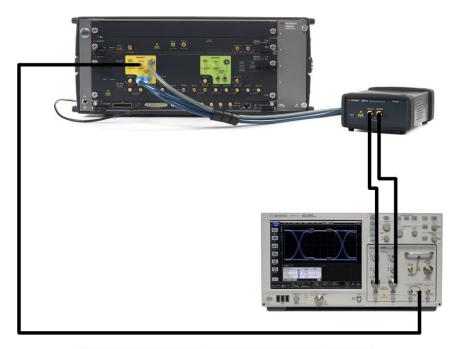

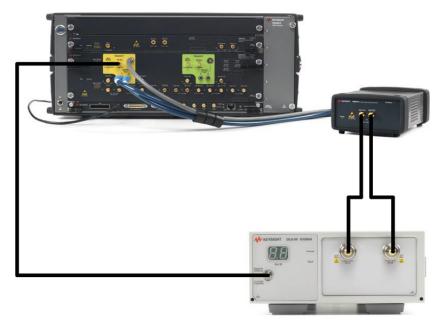

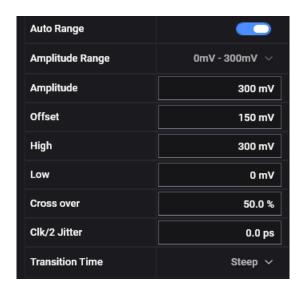

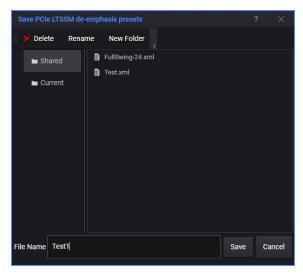

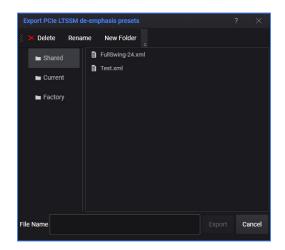

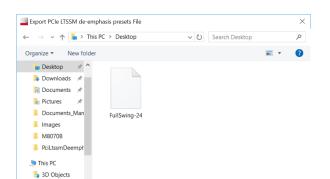

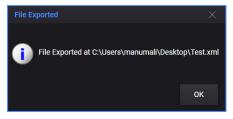

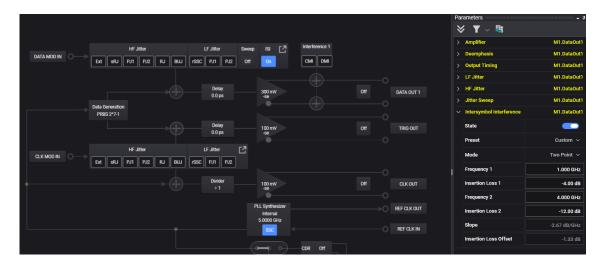

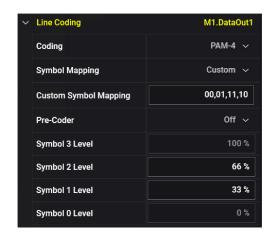

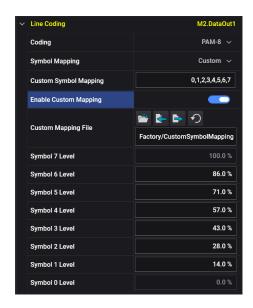

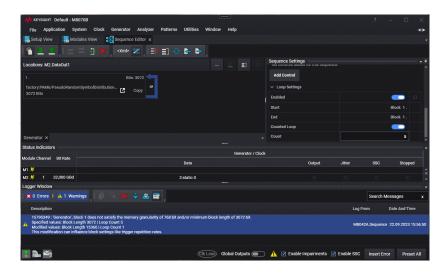

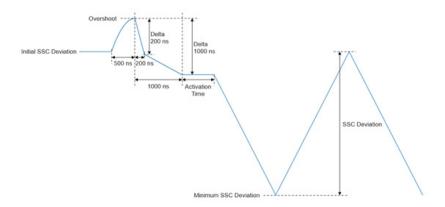

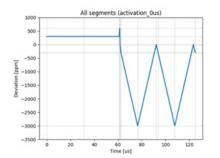

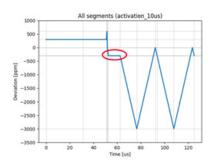

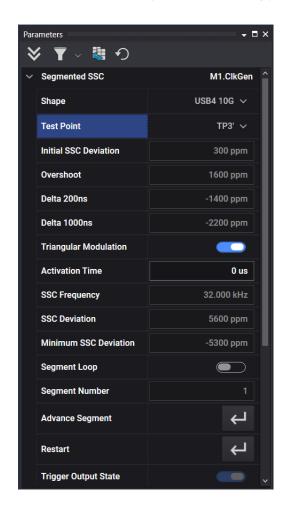

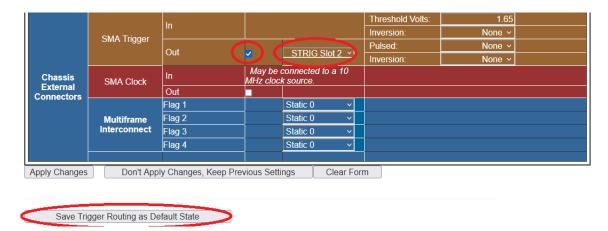

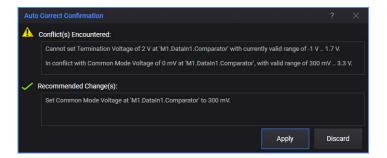

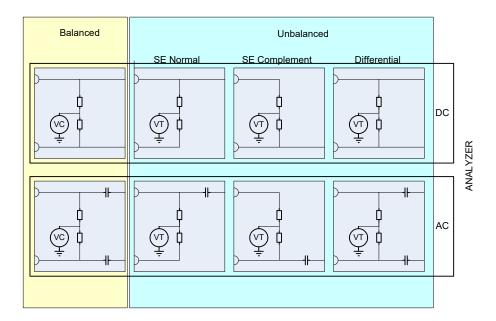

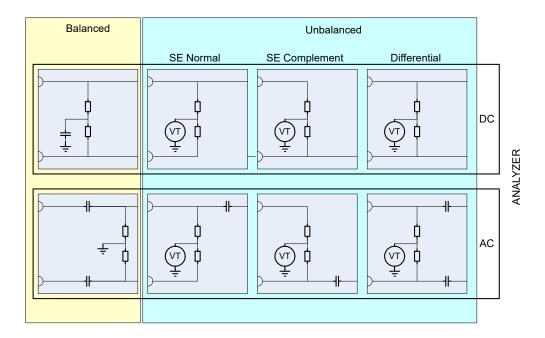

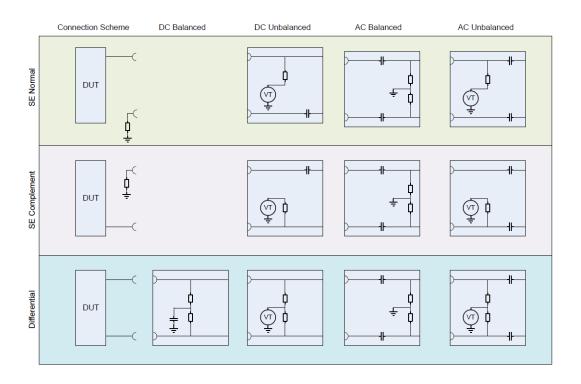

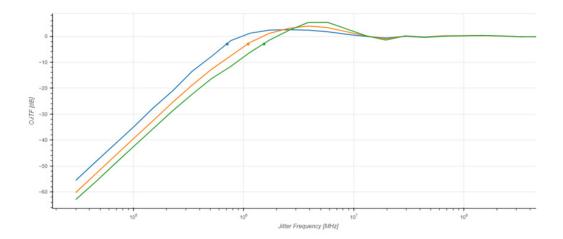

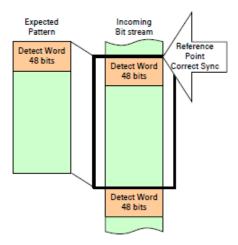

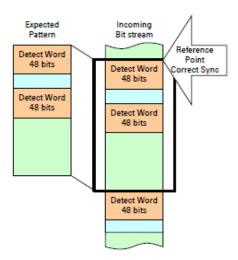

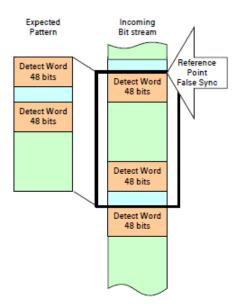

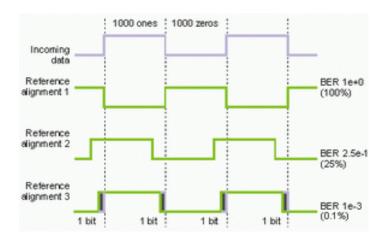

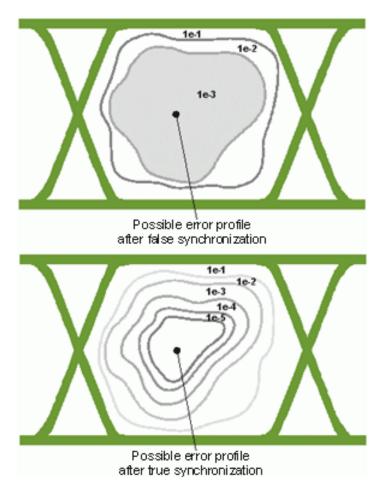

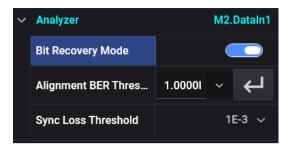

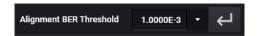

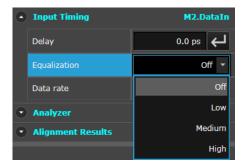

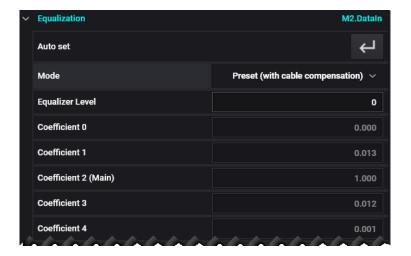

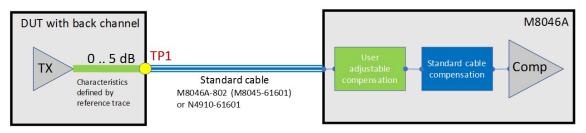

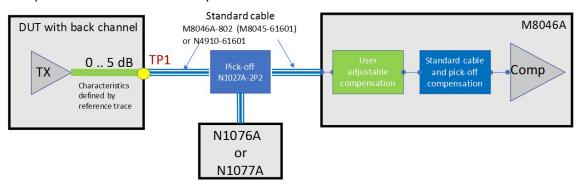

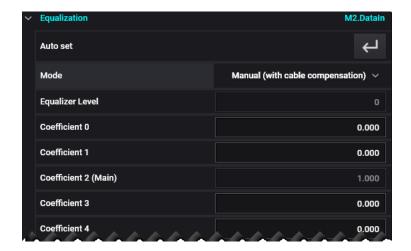

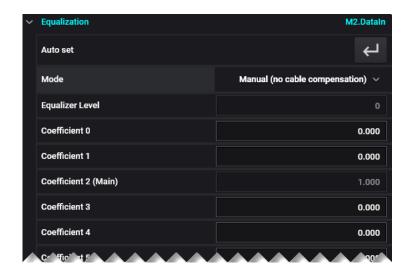

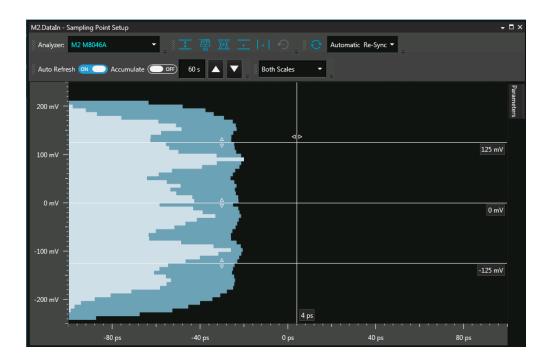

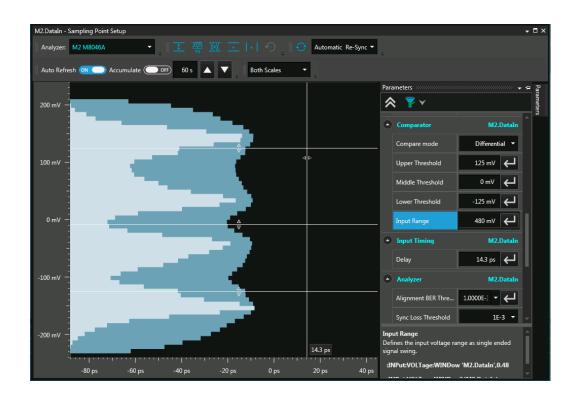

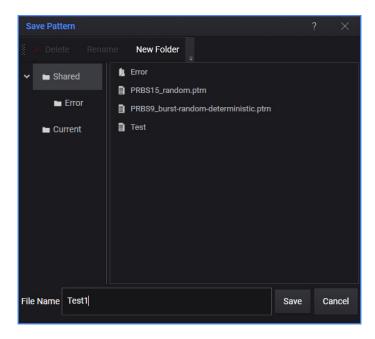

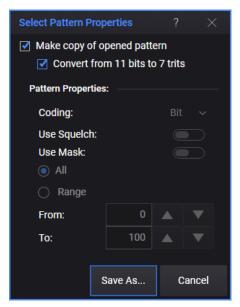

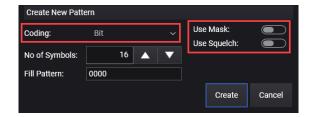

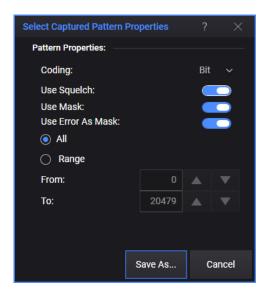

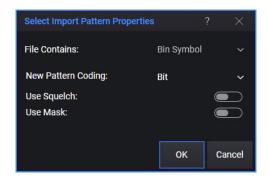

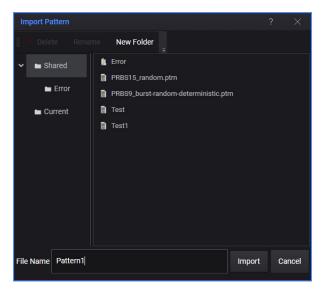

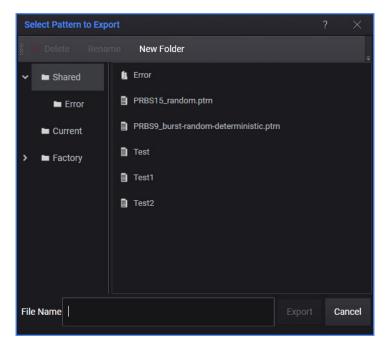

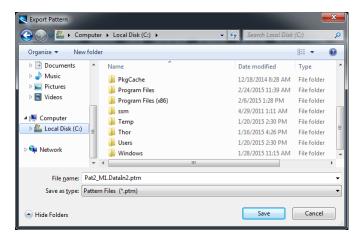

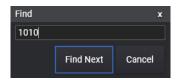

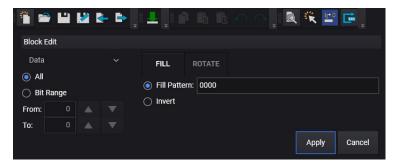

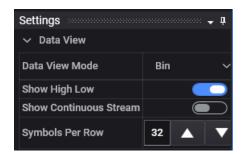

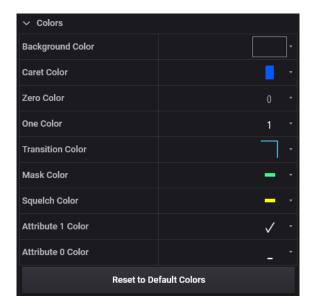

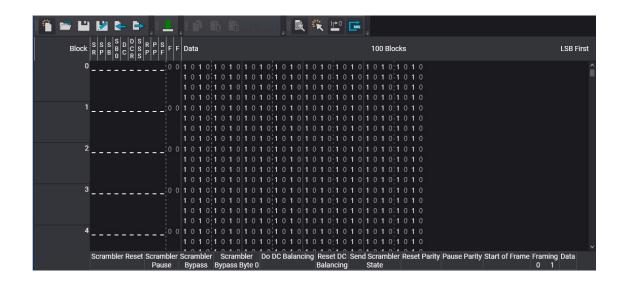

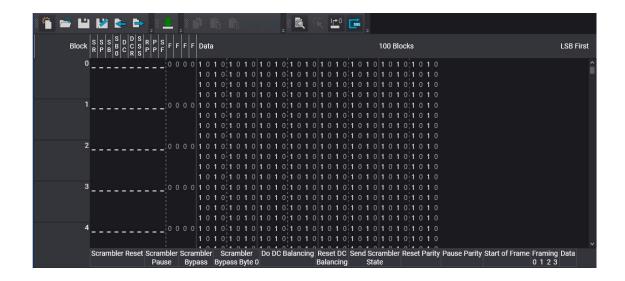

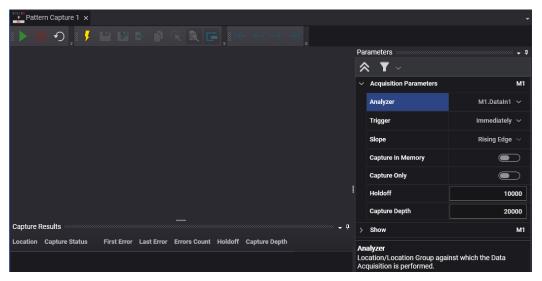

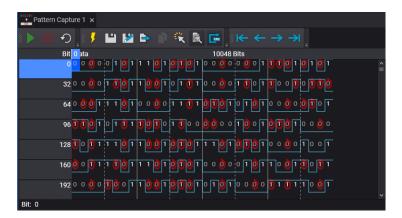

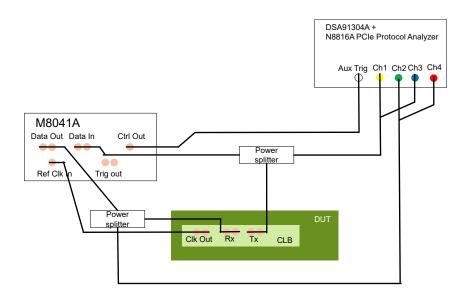

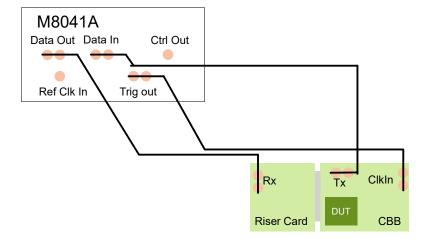

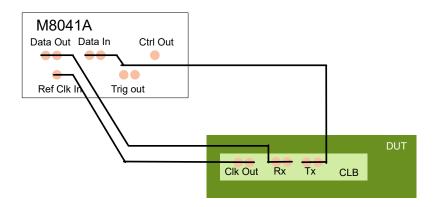

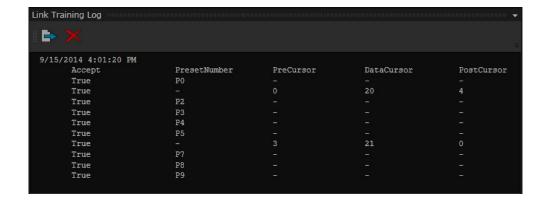

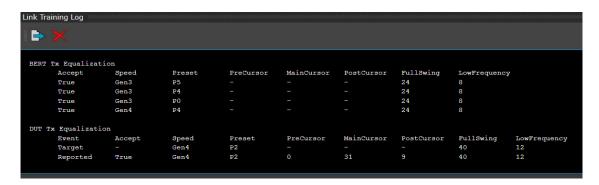

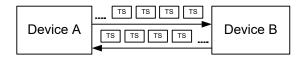

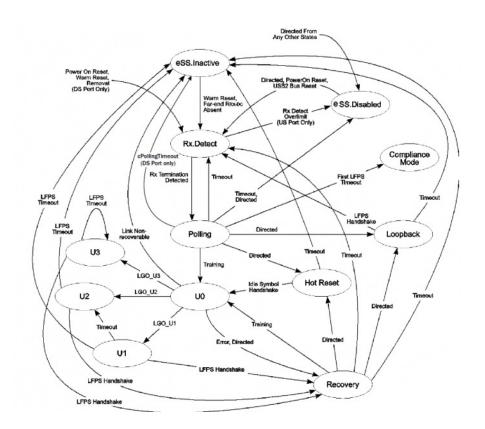

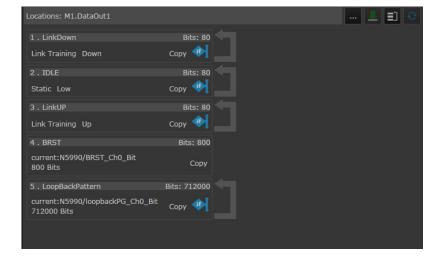

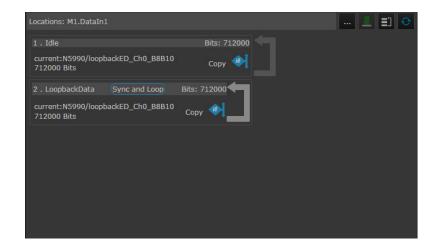

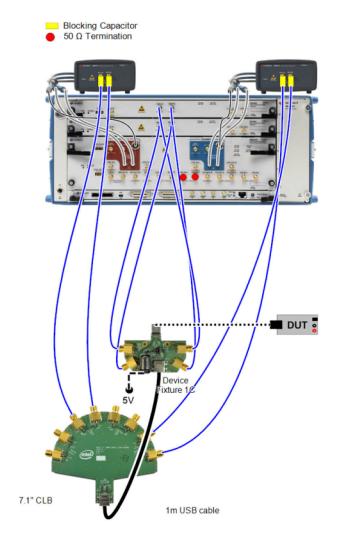

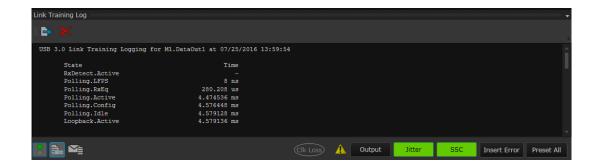

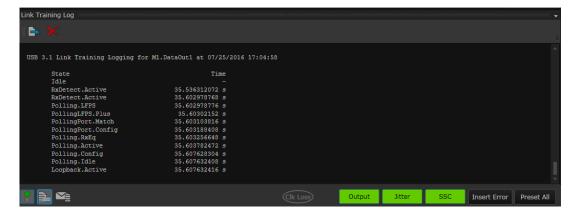

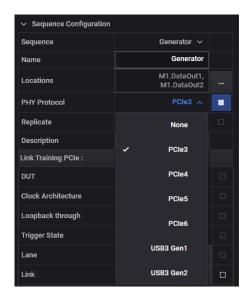

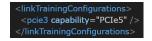

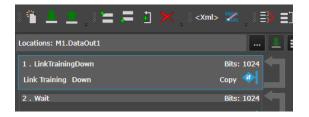

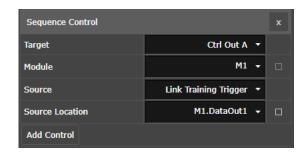

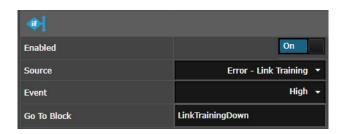

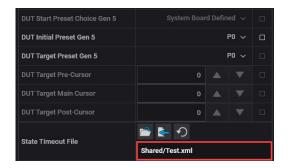

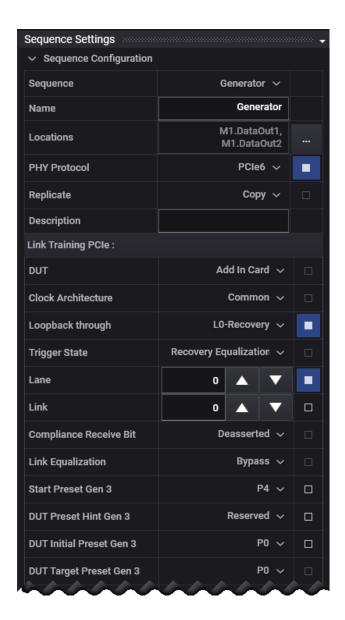

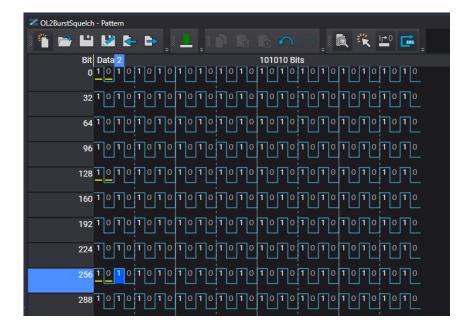

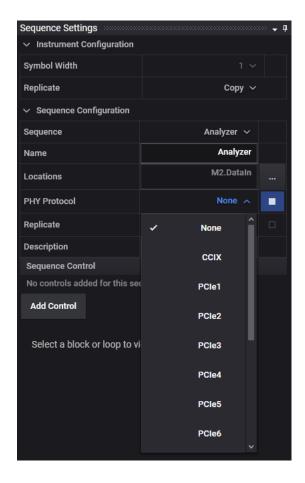

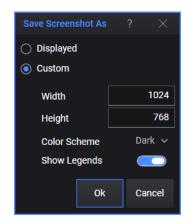

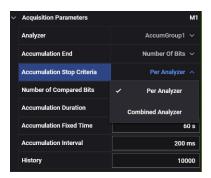

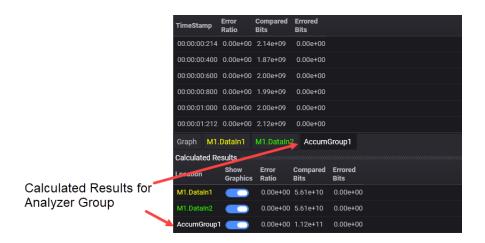

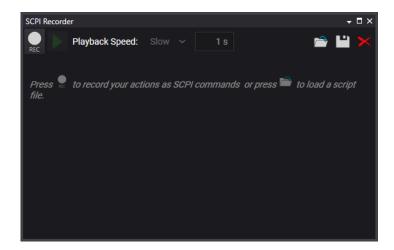

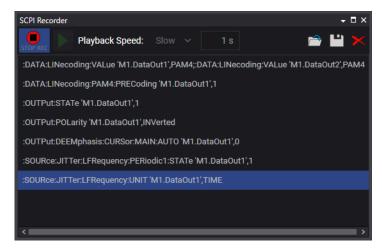

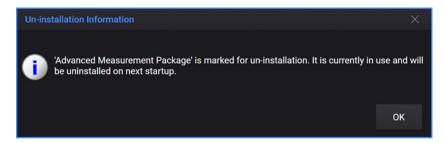

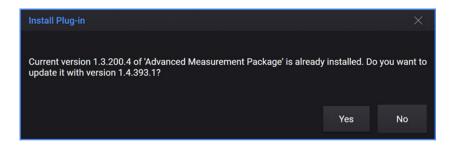

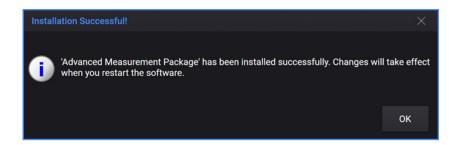

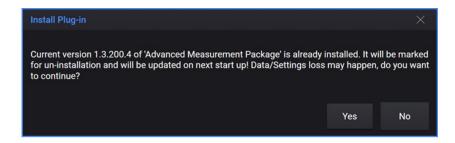

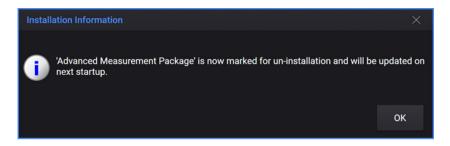

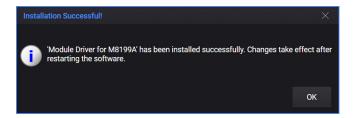

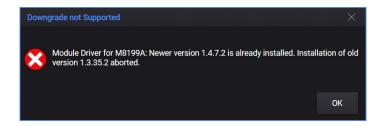

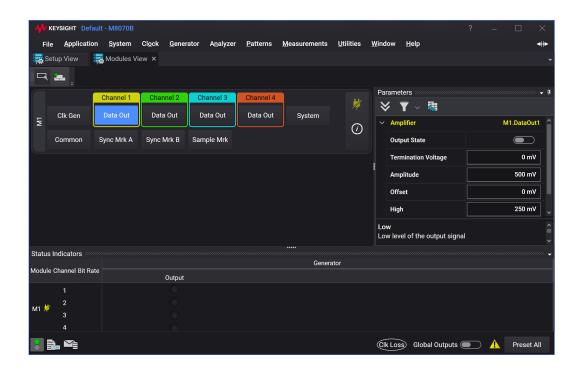

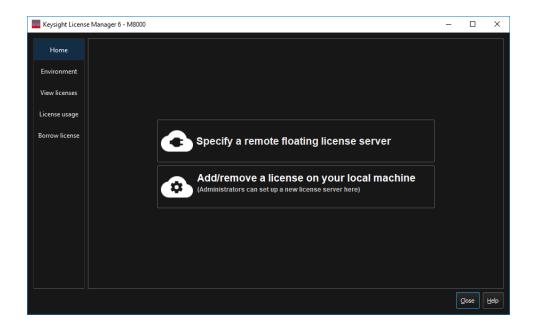

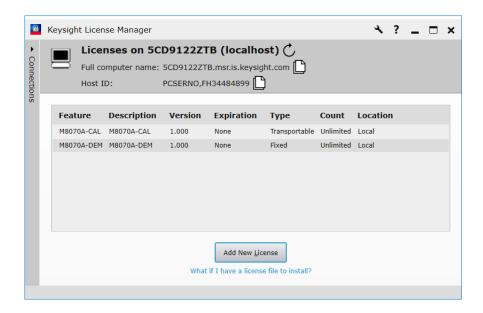

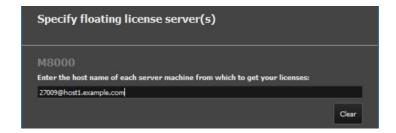

- synchronizes timing across all modules through the Keysight Trigger Bus, using an internal or external clock source.