User Guide

Keysight N4960A Serial BERT 17 and 32 Gb/s

### **Notices**

© Keysight Technologies, Inc. 2012-2019

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies, Inc. as governed by United States and international copyright laws.

#### Manual Part Number

N4960-91021

#### Edition

Edition 9.0, April 2019

Printed in Germany

Keysight Technologies, Inc. Keysight Technologies R&D and Marketing-GmbH & Co. KG Herrenberger Str. 130 71034 Böblingen, Germany

#### Warranty

THE MATERIAL CONTAINED IN THIS DOCUMENT IS PROVIDED "AS IS," AND IS SUBJECT TO BEING CHANGED, WITHOUT NOTICE, IN FUTURE EDITIONS. FURTHER, TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, KEYSIGHT DISCLAIMS ALL WARRANTIES, EITHER EXPRESS OR IMPLIED WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED HEREIN, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, KEYSIGHT SHALL NOT BE LIABLE FOR ERRORS OR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE, OR PERFORMANCE OF THIS DOCUMENT OR ANY INFORMATION CONTAINED HEREIN. SHOULD KEYSIGHT AND THE USER HAVE A SEPARATE WRITTEN AGREEMENT WITH WARRANTY TERMS COVERING THE MATERIAL IN THIS DOCUMENT THAT CONFLICT WITH THESE TERMS, THE WARRANTY TERMS IN THE SEPARATE AGREEMENT WILL CONTROL.

#### Technology Licenses

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

#### Restricted Rights Legend

If software is for use in the performance of a U.S. Government prime contract or subcontract, Software is delivered and licensed as "Commercial computer software" as defined in DFAR 252.227-7014 (June 1995), or as a "commercial item" as defined in FAR 2.101(a) or as "Restricted computer software" as defined in FAR 52.227-19 (June 1987) or any equivalent agency regulation or contract clause. Use, duplication or disclosure of

Software is subject to Keysight Technologies' standard commercial license terms, and non-DOD Departments and Agencies of the U.S. Government will receive no greater than Restricted Rights as defined in FAR 52.227-19(c)(1-2) (June 1987). U.S. Government users will receive no greater than Limited Rights as defined in FAR 52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2) (November 1995), as applicable in any technical data.

#### Safety Notices

#### CAUTION

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

#### WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

# **Safety Summary**

The following general safety precautions must be observed during all phases of operation of this instrument. Failure to comply with these precautions or with specific warnings or operating instructions in the product manuals violates safety standards of design, manufacture, and intended use of the instrument. Keysight Technologies assumes no liability for the customer's failure to comply with these requirements. Product manuals are provided with your instrument on CD-ROM and/or in printed form. Printed manuals are an option for many products. Manuals may also be available on the Web. Go to www.keysight.com and type in your product number in the Search field at the top of the page.

#### General

This product is a Safety Class 1 instrument (provided with a protective earth terminal). The protective features of this product may be impaired if it is used in a manner not specified in the operation instructions.

All Light Emitting Diodes (LEDs) used in this product are Class 1 LEDs as per IEC 60825-1.

#### **Environment Conditions**

This instrument is intended for indoor use in an installation category II, pollution degree 2 environment. It is designed to operate at a maximum relative humidity of 15 to 85% and at altitudes of up to 2000 meters.

Refer to the specifications tables for the ac mains voltage requirements and ambient operating temperature range.

#### Before Applying Power

Verify that all safety precautions are taken. The power cable inlet of the instrument serves as a device to disconnect from the mains in case of hazard. The instrument must be positioned so that the operator can easily access the power cable inlet. When the instrument is rack mounted the rack must be provided with an easily accessible mains switch.

#### Ground the Instrument

To minimize shock hazard, the instrument chassis and cover must be connected to an electrical protective earth ground. The instrument must be connected to the ac power mains through a grounded power cable, with the ground wire firmly connected to an electrical ground (safety ground) at the power outlet. Any interruption of the protective (grounding) conductor or disconnection of the protective earth terminal will cause a potential shock hazard that could result in personal injury.

## Do Not Operate in an Explosive Atmosphere

Do not operate the instrument in the presence of flammable gases or fumes.

# Do Not Remove the Instrument Cover

Operating personnel must not remove instrument covers. Component replacement and internal adjustments must be made only by qualified personnel.

Instruments that appear damaged or defective should be made inoperative and secured against unintended operation until they can be repaired by qualified service personnel.

# Safety Symbols

Table 1. Safety Symbol

| Symbol        | Description                                                                                                                                                                                                               |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\triangle$   | Indicates warning or caution. If you see this symbol on a product, you must refer to the manuals for specific Warning or Caution information to avoid personal injury or damage to the product.                           |

| <i>/</i>      | Frame or chassis ground terminal. Typically connects to the equipment's metal frame.                                                                                                                                      |

| <u> </u>      | Indicates hazardous voltages and potential for electrical shock.                                                                                                                                                          |

|               | Indicates that antistatic precautions should be taken.                                                                                                                                                                    |

|               | Indicates hot surface. Please do not touch.                                                                                                                                                                               |

| ● ∘           | CSA is the Canadian certification mark to demonstrate compliance with the Safety requirements.                                                                                                                            |

| CICES/NMB-001 | CE compliance marking to the EU Safety and EMC Directives. ISM GRP-1A classification according to the international EMC standard. ICES/NMB-001 compliance marking to the Canadian EMC standard.                           |

|               | The RCM mark indicates that this product meets EMS/Product Safety Requirements and may be imported to Australia and New Zealand.                                                                                          |

| ICES/NMB-001  | This mark indicates compliance with the Canadian EMC regulations.                                                                                                                                                         |

| ISM 1-A       | This text denotes the instrument is an Industrial Scientific and Medical Group 1 Class A product.                                                                                                                         |

|               | China RoHS regulations include requirements related to packaging, and require compliance to China standard GB18455-2001. This symbol indicates compliance with the China RoHS regulations for paper/fiberboard packaging. |

| 40)           | Indicates the time period during which no hazardous or toxic substance elements are expected to leak or deteriorate during normal use. Forty years is the expected useful life of the product.                            |

|               | The South Korean Class A EMC declaration (KC) mark indicates that this product is Class A suitable for professional use and is for use in electromagnetic environments outside of the home.                               |

|               | The KC mark includes the marking's identifier code that has up to 26 digits and follows this format: KCC-VWX-YYY-ZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZ                                                                        |

|               |                                                                                                                                                                                                                           |

# **Compliance and Environmental Information**

Table 2. Compliance and Environmental Information

| Safety Symbol | Description                                                                                                                                                                                        |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ø             | This product complies with WEEE Directive (2002/96/EC) marking requirements. The affixed label indicates that you must not discard this electrical/electronic product in domestic household waste. |

|               | Product Category: With reference to the equipment types in WEEE Directive Annex I, this product is classed as a "Monitoring and Control instrumentation" product.                                  |

|               | Do not dispose in domestic household waste.                                                                                                                                                        |

|               | To return unwanted products, contact your local Keysight office for more information.                                                                                                              |

# **Contents**

| 1 | Settir | ng Up the System                          | 11 |

|---|--------|-------------------------------------------|----|

|   | 1.1    | Rack Mount Kit                            | 11 |

|   | 1.2    | Unpacking                                 | 11 |

|   | 1.3    | Important Notes                           | 12 |

|   | 1.4    | Measurement Best Practices                | 12 |

|   | 1.5    | General Specifications                    | 13 |

|   | 1.6    | Safety and Regulatory                     |    |

|   | 1.7    | Installation                              | 15 |

| 2 | Opera  | ation Overview                            | 17 |

|   | 2.1    | Introduction                              | 17 |

|   | 2.2    | Features                                  | 17 |

|   | 2.3    | Control                                   | 19 |

|   | 2.4    | Introduction to Stress                    | 19 |

|   |        | 2.4.1 Quantifying Jitter                  |    |

|   |        | 2.4.2 Types of Jitter / Stress            |    |

|   |        | 2.4.3 Stress for Jitter Tolerance Testing | 24 |

| 3 | Opera  | ation                                     | 25 |

|   | 3.1    | General Information                       |    |

|   |        | 3.1.1 Performance Recommendations         |    |

|   |        | 3.1.2 Connector Care                      |    |

|   | 3.2    | Power on Settings                         | 26 |

|   | 3.3    | N4960A Serial BERT Controller Front Panel | 27 |

|   | 3.4    | N4960A Serial BERT Controller Rear Panel  | 30 |

|   | 3.5    | N4951A Front Panel                        | 31 |

|   | 3.6    | N4951A Rear Panel                         | 32 |

|   | 3.7    | N4951B-D17/-D32 Front Panel               | 33 |

|   | 3.8    | N4951B-D17/-D32 Rear Panel                | 34 |

|   | 3.9    | N4951B-H17/-H32 Front Panel               | 34 |

|   | 3.10   | N4951B-H17/-H32 Rear Panel                | 35 |

| 3.11 | N4952                                                                        | A Front Panel36                                                                                                                                                                                     |   |

|------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 3.12 | N4952                                                                        | A Rear Panel37                                                                                                                                                                                      |   |

| 3.13 | Block [                                                                      | Diagram (32 Gb/s system)38                                                                                                                                                                          |   |

| 3.14 | Block [                                                                      | Diagram (17 Gb/s system)39                                                                                                                                                                          |   |

| 3.15 | 3.15.1<br>3.15.2<br>3.15.3<br>3.15.4<br>3.15.5<br>3.15.6<br>3.15.7<br>3.15.8 | A Serial BERT Controller                                                                                                                                                                            | 5 |

| 3.16 | 3.16.1<br>3.16.2<br>3.16.3<br>3.16.4<br>3.16.5                               | Library of Patterns 48 Programmable Patterns 48 Error Injection 49 Pattern Generator Output Stage 50 Dual Pattern Generator Operation 50 N4951B-D17/-D32 Pattern Generator with 5-tap Deemphasis 51 |   |

| 3.17 | 3.17.1<br>3.17.2<br>3.17.3<br>3.17.4                                         | Detector                                                                                                                                                                                            |   |

| 3.18 | 3.18.1                                                                       | ate Clock Architecture                                                                                                                                                                              |   |

| 3.19 | 3.19.1                                                                       | or Rate Tests                                                                                                                                                                                       |   |

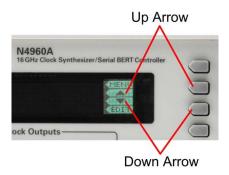

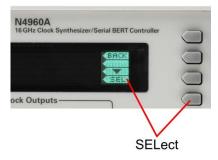

| 3.20 |                                                                              | l Panel Operation60 Menu Navigation60                                                                                                                                                               |   |

|   |         | 3.20.2 Changing Parameters                                         | 62  |

|---|---------|--------------------------------------------------------------------|-----|

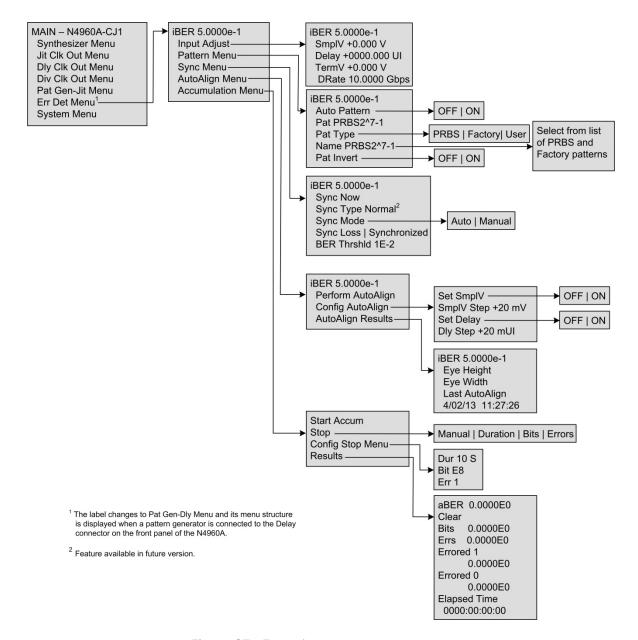

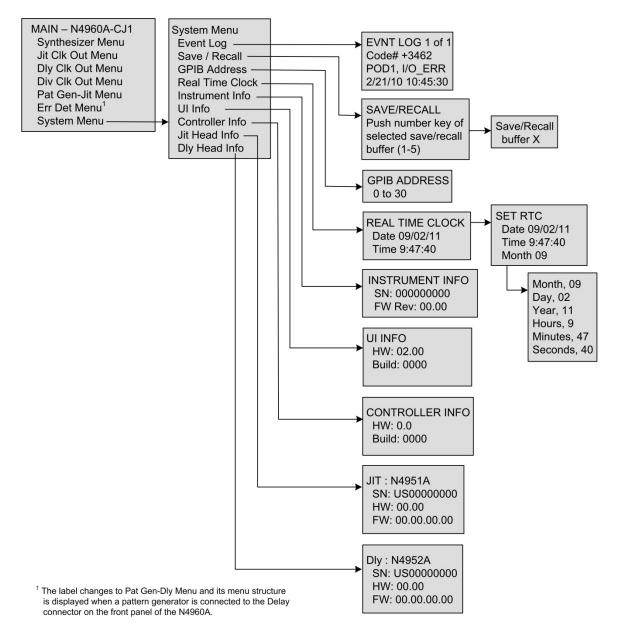

|   |         | 3.20.3 Menu Structure                                              |     |

|   |         | 3.20.4 Menu Label Descriptions                                     | 69  |

|   | 3.21    | Working with Setting Dependencies                                  | 83  |

|   | 3.22    | Verifying Operation                                                | 85  |

|   |         | 3.22.1 Initial Hardware Setup – Controller and Pattern             | 0 5 |

|   |         | Generator                                                          |     |

|   |         | 3.22.3 Enabling Sinusoidal Jitter                                  |     |

|   |         | 3.22.4 Enabling Random Jitter (N4960A-CJ1 controller only)         |     |

|   |         | 3.22.5 Enabling Spread Spectrum Clock (N4960A-CJ1 controller only) | 20  |

|   |         | 3.22.6 Bit Error Rate Test                                         |     |

|   | 3.23    | Setting Frequency and Output Amplitude                             |     |

|   | 3.24    | Setting Random Jitter Injection (N4960A-CJ1 controller only)       | 93  |

|   | 3.25    | Setting Sinusoidal Jitter Injection                                | 93  |

|   | 3.26    | Setting External Jitter High Frequency Injection                   | 94  |

|   | 3.27    | Setting Delay Clock Output                                         | 94  |

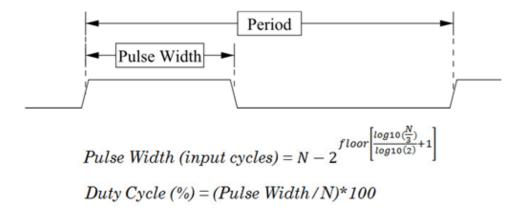

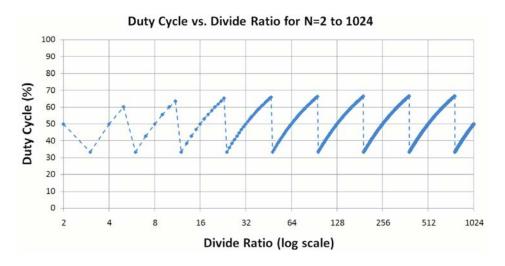

|   | 3.28    | Setting Divided Clock Output                                       | 95  |

|   | 3.29    | Event/Error Log                                                    | 96  |

| 4 | Applica | ations                                                             | .97 |

|   | 4.1     | Introduction                                                       | 97  |

|   | 4.2     | Testing Transceivers Used in Fibre Channel Networks                | 98  |

| 5 | Perforr | mance Specifications1                                              | 101 |

|   | 5.1     | N4960A Clock Source/BERT Controller Non-stressed Specifications    | 101 |

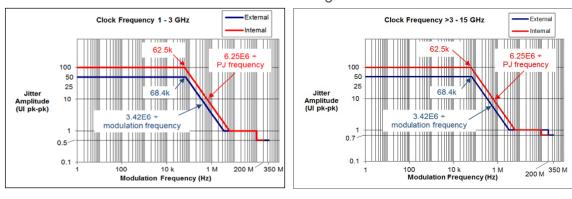

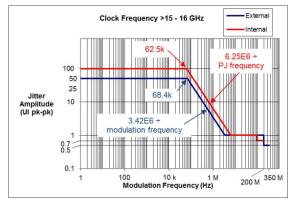

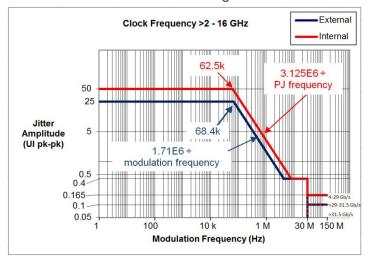

|   | 5.2     | N4960A Clock Source/BERT Controller Jitter Specifications . 1      | 103 |

|   |         | 5.2.1 Maximum N4960A Clock Modulation Range without P Connected    |     |

|   |         | 5.2.2 Maximum N4960A Clock Modulation Range with PG Connected      | 107 |

|   | 5.3     | N4951A/N4951B <sup>7</sup> Pattern Generator Specifications        | 108 |

|   | 5.4     | N4952A-E17/N4952A-E32 Error Detector Specifications 1              | 111 |

|   |         |                                                                    |     |

| 6 | Remot  | te Operation113                                               |

|---|--------|---------------------------------------------------------------|

|   | 6.1    | GPIB Interface                                                |

|   | 6.2    | USB Interface114                                              |

|   |        | 6.2.1 USB Driver                                              |

|   |        | 6.2.2 USB Programming Note                                    |

|   | 6.3    | Remote Command Syntax                                         |

|   |        | 6.3.1 Command Structure                                       |

|   | 6.4    | IEEE Common Commands                                          |

|   | 6.5    | SCPI Mandated Commands                                        |

|   | 6.6    | SCPI Protocol Description                                     |

|   |        | 6.6.1 SCPI Example                                            |

|   | 6.7    | SCPI Numeric Parameters and Optional Units119                 |

|   | 6.8    | Pattern Generator Channelization                              |

|   | 6.9    | Command Conventions                                           |

|   | 6.10   | SCPI Standard Negative Event/Error Codes                      |

|   |        | 6.10.1 "Settings Conflict" Used for Settings Dependencies 122 |

|   | 6.11   | N4960A Serial BERT Controller Device Commands 123             |

|   | 6.12   | Pattern Generator Device Commands                             |

|   | 6.13   | Error Detector Device Commands                                |

|   | 6.14   | Command Summary                                               |

|   |        | 6.14.1 N4960A Serial BERT Controller Command Summary 208      |

|   |        | 6.14.2 Pattern Generator Command Summary                      |

|   | 0.15   | 6.14.3 Error Detector Command Summary                         |

|   | 6.15   | Programming Example                                           |

|   | 6.16   | Programming Tips                                              |

|   |        | 6.16.1 Example Using *OPC?                                    |

|   |        | 6.16.3 Communication Timeouts                                 |

| 7 | Returr | ning the N4960A to Keysight233                                |

| 8 | Appen  | ndix A Preset State235                                        |

# 1 Setting Up the System

The N4960A serial BERT controller 17 and 32 Gb/s is shipped in a protective box. Each shipping box contains:

- N4960A-CJ0 or N4960A-CJ1 serial BERT controller.

- AC power cord.

- CD-ROM, which includes:

- o N4960A Serial BERT 17 and 32 Gb/s user guide

- o N4960A Serial BERT 17 and 32 Gb/s getting started guide

- o N4960A Serial BERT 17 and 32 Gb/s datasheet

The N4951A, N4951B, and N4952A are shipped in protective boxes with all the accessories required for operation. Each shipping box contains:

- N4951A, N4951B, or N4952A with remote head/controller cable.

- CD-ROM, which includes:

- o N4960A Serial BERT 17 and 32 Gb/s user guide

- o N4960A Serial BERT 17 and 32 Gb/s getting started guide

- o N4960A Serial BERT 17 and 32 Gb/s datasheet

#### 1.1 Rack Mount Kit

The optional N4978A rack mount kit can be purchased separately for rack mounting the N4960A as a single unit or two instruments mounted side-by-side.

# 1.2 Unpacking

Carefully remove the instrument from the packaging in an ESD-safe environment.

# 1.3 Important Notes

- Use ESD protection at all times when using the instrument.

- Before connecting any cable to the instrument, discharge the cable by shorting the center and outer connectors of the cable together to ground momentarily.

- Review min/max specifications before applying input signals.

- Use high quality connectors on all ports. The N4951A pattern generator output and N4952A error detector input connectors are 2.92 mm, while all clock output and input connectors on the N4960A serial BERT controller are SMA. The N4951B pattern generator data output connectors are 2.4 mm.

- Leave dust jackets on unused back panel connectors.

- Situate the instrument away from heat sources, do not block the fans, and do not block the exhaust vents on the sides of the BERT controller and remote heads (minimum of 3 inches clearance).

- The bottom of a remote head can become hot to the touch. The airflow should not be blocked as this will increase the temperature.

- Power must be turned off before connecting/disconnecting a remote head.

# 1.4 Measurement Best Practices

- When using differential-mode connections, ensure the cables are phase balanced for best performance.

- Use high quality cables and connector savers (or adaptors).

- Keep cable lengths short and minimize the number of cable bends.

- Use an 8 in-lbs (90 N-cm) torque wrench when attaching connectors.

# 1.5 General Specifications

Before installing the N4960A serial BERT, review the specifications in Table 3.

Table 3. Specification considerations before installation

| Parameter                                 | Specification                                                             |

|-------------------------------------------|---------------------------------------------------------------------------|

| Connector Type                            |                                                                           |

| Controller                                |                                                                           |

| All signals except 10 MHz Ref<br>In/Out – | SMA                                                                       |

| 10 MHz In/Out                             | BNC                                                                       |

| N4951A/N4952A                             | 2.92 mm female                                                            |

| N4951B                                    | 2.4 mm female (data output connectors), SMA female (auxiliary connectors) |

| Remote Control Interface                  | USB2.0 and IEEE-488 (GPIB)                                                |

| Operating Temperature                     | +15 °C to +35 °C                                                          |

| Storage Temperature                       | -40 °C to +70 °C                                                          |

| Line Power                                |                                                                           |

| Voltage                                   | 100 to 240 VAC autoranging                                                |

| Frequency                                 | 50/60 Hz                                                                  |

| Power                                     | 170 Watts MAX                                                             |

| Fuse                                      | 250 V 2 A 5x20 mm (p/n 12260-002)                                         |

|                                           | Always replace instrument fuse with one of the same type and rating.      |

| Dimensions (Height, Width, and Depth)     |                                                                           |

| N4960A                                    | 100 mm (3.9 in) x 214 mm (16.7 in) x 425 mm (16.7 in)                     |

| N4951A/N4952A                             | 50 mm (1.9 in) x 109 mm (4.3 in) x 222 mm (8.7 in)                        |

| N4951B                                    | 50 mm (1.9 in) x 109 mm (4.3 in) x 273 mm (10.75 in)                      |

| Remote head/controller cable              | 1.0 m (39.7 in)                                                           |

| Weight                                    |                                                                           |

| N4960A                                    | 3.2 kg (7.0 lbs)                                                          |

| N4951A/N4952A (with cable)                | 0.86 kg (30.3 oz)                                                         |

| N4951B (with cable)                       | 1.0 kg (35.3 oz)                                                          |

| Parameter | Specification                                                                                                                                                                                                                                                            |                                     |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| EMC       | <ul> <li>Complies with European</li> <li>IEC/EN 61326-1</li> <li>CISPR Pub 11 Group 1</li> <li>AS/NZS CISPR 11</li> <li>ICES/NMB-001</li> <li>This ISM device complies with C</li> </ul>                                                                                 |                                     |

|           | Cet appareil ISM est conforme a                                                                                                                                                                                                                                          |                                     |

| Safety    | <ul> <li>Complies with European 2006/95/EC</li> <li>IEC/EN 61010-1, 2nd E</li> <li>Canada: CSA C22.2 No.</li> <li>USA: UL std no. 61010-Acoustic noise emission Gerae LpA &lt;70 dB</li> <li>Operator position</li> <li>Normal position</li> <li>Per ISO 7779</li> </ul> | dition<br>61010-1<br>1, 2nd Edition |

# 1.6 Safety and Regulatory

This product has been designed and tested in accordance with accepted industry standards, and has been supplied in a safe condition. The documentation contains information and warnings that must be followed by the user to ensure safe operation and to maintain the product in a safe condition.

#### WARNING

Do not remove instrument covers. There are no user serviceable parts within. Operation of the instrument in a manner not specified by Keysight Technologies may result in personal injury or loss of life.

#### WARNING

For continued protection against fire hazard, replace fuses, and or circuit breakers only with same type and ratings. The use of other fuses, circuit breakers or materials is prohibited.

#### WARNING

To prevent electrical shock, disconnect instrument from mains before cleaning. Use a dry cloth or one slightly dampened with water to clean the external case parts. Do not attempt to clean internally.

#### CAUTION

The Mains wiring and connectors shall be compatible with the connector used in the premise electrical system. Failure, to ensure adequate earth grounding by not using the correct components may cause product damage, and serious injury.

### 1.6.1 Declaration of Conformity

A EU declaration of conformity is available at <a href="http://regulations.corporate.Keysight.com/doc/search.htm">http://regulations.corporate.Keysight.com/doc/search.htm</a>

### 1.7 Installation

The following procedure describes how to install the N4960A serial BERT.

- 1. Install on a flat surface with unobstructed airflow to the back panel and side vents.

- 2. Plug the AC power cord into a suitable wall socket (100 to 240 V AC, 50/60 Hz).

#### WARNING

If this product is not used as specified, the protection provided by the equipment could be impaired. This product must be used in a normal condition (in which all means for protections are intact) only.

- 3. Plug the AC power cord into the N4960A serial BERT.

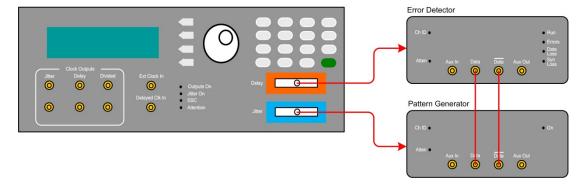

- 4. Connect the pattern generator to the Jitter connector on the front panel.

- 5. Connect the error detector or a pattern generator to the Delay connector on the front panel.

| _ | A | - | _ | ^ |  |

|---|---|---|---|---|--|

|   |   | _ | _ |   |  |

|   |   |   | _ | w |  |

|   |   |   |   |   |  |

Before switching on this instrument, make sure the supply voltage is in the specified range.

# CAUTION

This instrument has autoranging line voltage input. Be sure the supply voltage is within the specified range.

# 2 Operation Overview

#### 2.1 Introduction

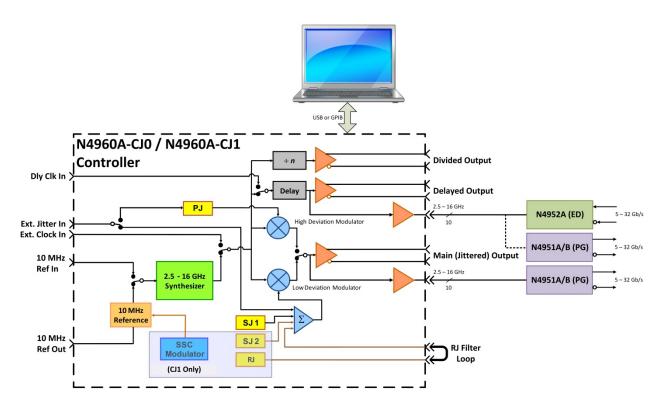

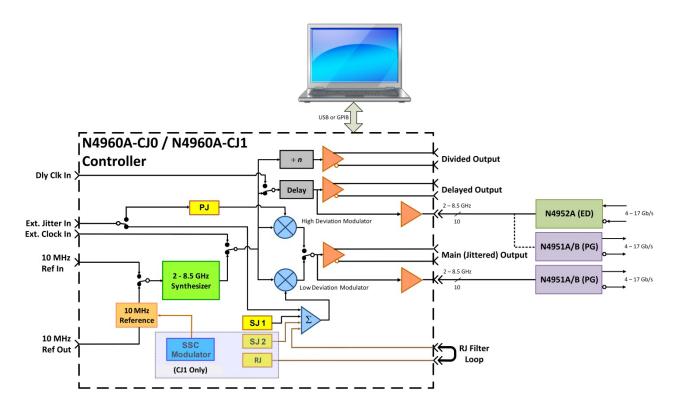

The N4960A serial BERT consists of a controller, which is a stressed clock source with multi-sourced jitter capability, and support for an externally connected pattern generator and error detector to form a BERT. When used as a clock synthesizer, the range is 1 to 16 GHz. When used with a remote head attached, the range of the clock synthesizer is 2.5 to 16 GHz for the 32 Gb/s system, or 2 to 8.5 GHz for the 17 Gb/s system. The pattern generator and error detector remote heads use half rate clock architecture, giving a data rate range of 5 to 32 Gb/s for the 32 Gb/s system, or 4 to 17 Gb/s for the 17 Gb/s system.

## 2.2 Features

All features can be controlled through the control panel, remotely through the GPIB or USB interface using the remote commands, or through the N4980A multi-instrument BERT software.

- Controller (stressed clock synthesizer)

- o Operation from 2.5 to 16 GHz (32 Gb/s system)

- o Operation from 2 to 8.5 GHz (17 Gb/s system)

- Two independent sinusoidal jitter injection sources (one for N4960A-CJ0)

- o True Gaussian random jitter stress (N4960A-CJ1 only)

- o Spread spectrum clock (N4960A-CJ1 only)

- o Fully programmable clock output parameters

- o Low intrinsic jitter

- o Jittered, non-jittered, and divided outputs

- o Remote control through GPIB (IEEE 488.2) or USB2.0

- o User interface along with SCPI command set for easy automation and test system integration

- N4951A-P17/N4951A-P32 programmable pattern generator

- o N4951A-P32 data rate from 5 Gb/s to 32 Gb/s

- o N4951A-P17 data rate from 4 Gb/s to 17 Gb/s

- o 1 V (p-p) output voltage (single-ended)

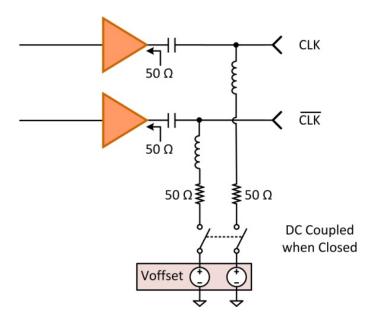

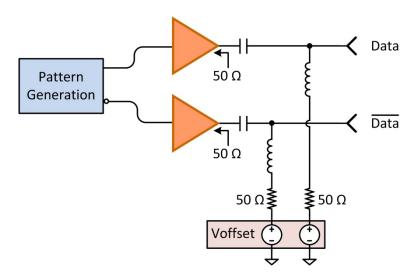

- o Single ended or differential AC coupled data output with integrated bias tee

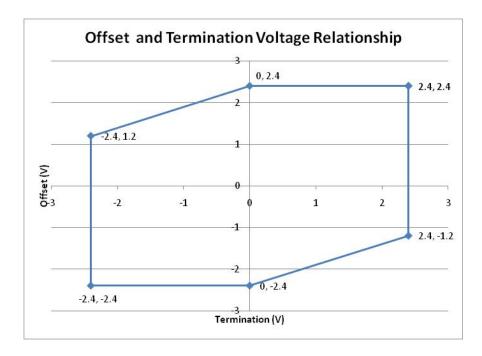

- o User definable offset and termination voltage

- o Family of PRBS patterns and predefined sample patterns

- o User programmable patterns (up to 8 Mbit memory depth)

- N4951B-D17/N4951B-D32 programmable pattern generator

- o N4951B-D32 data rate from 5 Gb/s to 32 Gb/s

- o N4951B-D17 data rate from 4 Gb/s to 17 Gb/s, 1.5 V (p-p) output voltage (single-ended)

- o 5-tap de-emphasis

- o Single ended or differential AC coupled data output with integrated bias tee

- o User definable offset and termination voltage

- o Family of PRBS patterns and predefined sample patterns

- o User programmable patterns (up to 8 Mbit memory depth)

- N4951B-H17/N4951B-H32 programmable pattern generator

- o N4951B-H32 data rate from 5 Gb/s to 32 Gb/s

- o N4951B-H17 data rate from 4 Gb/s to 17 Gb/s

- o 3 V (p-p) output voltage (single-ended)

- o Single ended or differential AC coupled data output with integrated bias tee

- o User definable offset and termination voltage

- o Family of PRBS patterns and predefined sample patterns

- o User programmable patterns (up to 8 Mbit memory depth)

- N4952A-E17/N4952A-E32 programmable error detector

- o N4952A-E32 data rate from 5 Gb/s to 32 Gb/s

- o N4952A-E17 data rate from 4 Gb/s to 17 Gb/s

- o Auto sample voltage and delay alignment (can be manually set)

- o Auto detects PRBS patterns

- o Single ended or differential AC coupled data input

- o User definable termination voltage

## 2.3 Control

System configuration settings are all available from the local control panel interface, the remote GPIB (IEEE 488.2) interface, or the USB interface. Instrument status is conveyed on the front panel by the display.

The N4960A serial BERT is supported by the N4980A multi-instrument BERT software Version 2.2 or higher, which provides a complete user control interface and off line pattern editing and management tool.

#### 2.4 Introduction to Stress

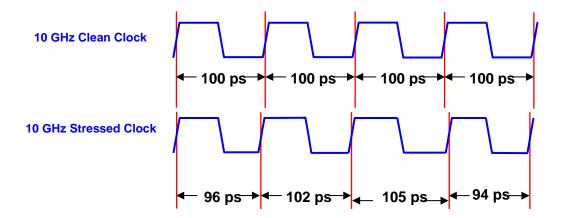

The N4960A serial BERT controller contains a stressed clock synthesizer. The term "Stress" refers to the ability to modulate the output signal with a calibrated level of timing jitter. Timing jitter is the short term variation of a signal with respect to its ideal position in time. Timing jitter can be seen and measured at the signal logic state transitions.

Figure 1. Timing Jitter

Amplitude jitter, also known as "interference" or simply noise, will act on the finite rise and fall times of transitions to produce effective timing jitter. The N4960A serial BERT controller does not generate interference (amplitude jitter). From this point forward, the term timing jitter will be reduced to simply jitter.

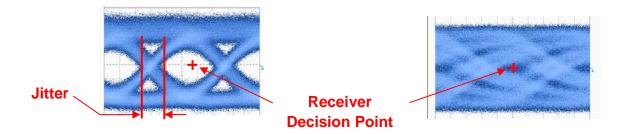

In serial data systems, excessive jitter acts to "close the eye" which will eventually result in bit errors, as the bit transition moves closer to the receiver's decision point time window.

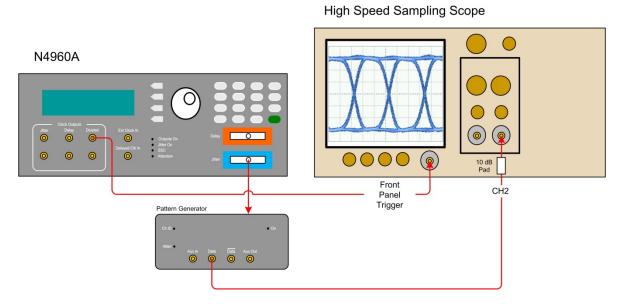

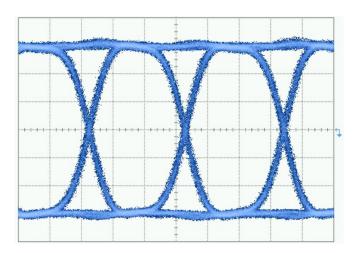

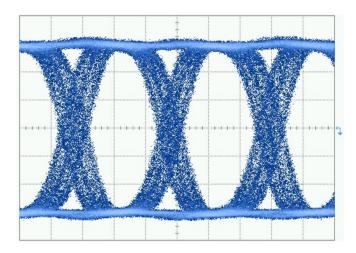

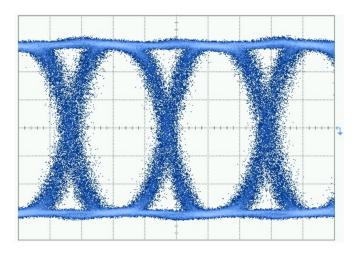

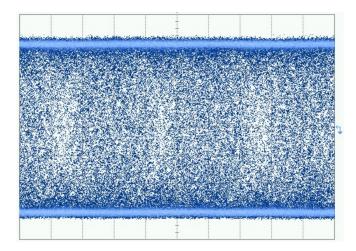

Figure 2. Eye closure with low (left) and high level of jitter (right)

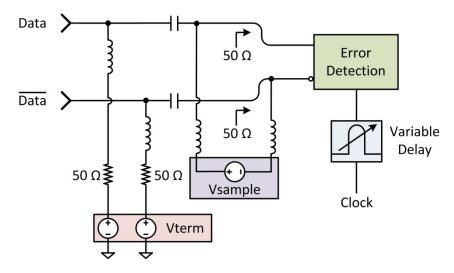

A common test for a serial data receiver is its susceptibility to jitter. The test is performed by driving a known data pattern into the receiver using the N4951A/N4951B pattern generator which is stressed with a known amount of jitter. The received data is compared to an internal reference pattern of the N4952A error detector, and the number of incorrect detected bits is counted. By varying the characteristics of the jitter used to modulate the test data generator, the receiver's performance can be characterized.

# 2.4.1 Quantifying Jitter

The level or "amplitude" of jitter refers to the instantaneous displacement in time of the measure point (transition) from its ideal location. When applied to a stress generator, the amplitude refers to a level of reoccurring jitter, rather than a single instantaneous edge displacement. The jitter amplitude will be stated as a peak to peak displacement, or a root means squared (rms) value, depending on the nature of the jitter distribution.

## 2.4.2 Types of Jitter / Stress

The jitter that a serial data receiver is exposed to in an operating environment is a composite of several elemental types. These types correspond to mechanisms in the environment which create the jitter, and are duplicated in the data pattern generator clock used to test a receiver.

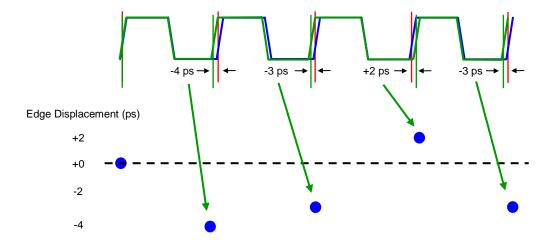

The "type" of jitter represents its distribution when looking at a continuous measurement of edge displacement over time. The representation of this is a time interval error (TIE) plot. The TIE plot is a graph of the absolute displacement of each transition edge in the jittered waveform with respect to its ideal location versus time (or bit location).

Figure 3. Time Interval Error plot of edge displacement

The resulting TIE plot shows the modulation of the jitter. The wave shape of the modulation envelope (TIE plot), relates to the type of jitter in the signal.

Jitter can be qualified as being one of a combination of several types, which again refer to the wave shape of the deviation versus time. The most basic distinction is deterministic versus non-deterministic. As its name implies, deterministic jitter forms a pattern which can be recognized. Deterministic jitter can be further broken down into data dependent, which is synchronous to the data pattern, and periodic, which has frequency components that are asynchronous to the data. While periodic jitter can have any wave shape, sinusoidal (SJ) is the most common.

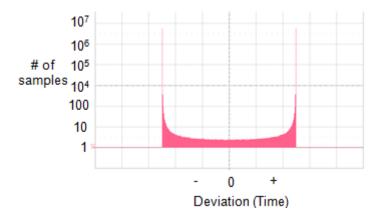

The jitter amplitude (deviation in time from ideal location) of deterministic jitter is bounded. Once enough transition edges have been sampled to determine the peaks of the TIE envelope, additional sampling will not show an increase in the peak instantaneous jitter. A common graphical representation of jitter is referred to as a TIE histogram, or simply a jitter histogram. The histogram shows peak deviation versus number of samples. Figure 4 shows a typical TIE histogram plot of sinusoidal jitter.

Figure 4. TIE histogram of pure sinusoidal jitter

The horizontal axis is jitter magnitude—deviation in time of the actual edge location relative to its ideal location. The axis has polarity, with 0 deviation occurring in the center. Points to the right of center are from transitions which occur after the ideal location (lag), while those to the left of center occur before the ideal location (lead).

The vertical axis shows the number of occurrences, plotted on a log scale. The characteristic shape reflects what is expected from a sine wave. The amplitude is near the positive and negative peak for most of the time, and in the zero crossing point for the least amount of time.

Generating a jitter histogram of pure deterministic jitter with a measurement instrument which updates the plot as additional samples are taken would quickly fill out the envelope, with no change in shape or peaks as additional samples are taken.

Because deterministic jitter is bounded, its magnitude is usually expressed as a peak to peak value. The units are either absolute time, for example picoseconds (ps), or relative to bit time, in unit intervals (UI).

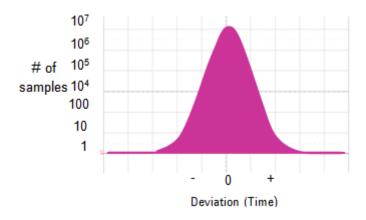

Non-deterministic jitter is composed primarily of random jitter components. As the name implies, the envelope of random jitter will have no recognizable pattern. Random jitter results from noise artifacts in the system. Non-deterministic jitter is un-bounded. As more samples are measured, the TIE histogram will show ever increasing peak jitter, occurring at small number of samples, with the process unending. The TIE histogram of pure random jitter (RJ) will have a true Gaussian deviation, as shown in Figure 5.

Figure 5. Typical TIE Histogram of Random Jitter

When only random jitter is present in the signal, the majority of transitions will occur at the ideal location in time (zero deviation), with decreasing numbers of transitions occurring at increasing levels of deviation in time. Due to the distribution, the magnitude of random jitter is usually expressed as a root mean squared (rms) value. The RJ magnitude can also be expressed as a peak to peak value, at a given confidence level. The confidence level can be computed from the number of samples. As with deterministic jitter, the units are either absolute time, for example ps, or relative to bit time, in UI.

Data and clock signals in real life operating systems will usually contain jitter which has both deterministic and non-deterministic components within it.

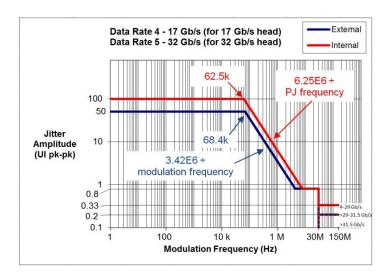

### 2.4.3 Stress for Jitter Tolerance Testing

Stressed clock synthesizers such as the N4960A serial BERT controller are used to clock a data pattern generator, which in turn is used to test a serial data receiver's susceptibility to jitter. The jitter tolerance test is the basic method generally used to characterize a receiver. The test is performed with a BERT, used to monitor the receiver detected output and determine when it does and when it does not operate error free. The test is started by operating the receiver and initializing the test setup to achieve error free operation. Then stress is added, usually as a single tone of SJ at a specific frequency with low amplitude. The SJ amplitude is increased until bit errors start to occur. The stress amplitude at this point is recorded, the SJ amplitude reduced and the frequency changed. The process then repeats at the new SJ frequency. The resulting jitter tolerance plot shows the limits of error free operation as jitter amplitude versus jitter frequency.

Some communication standards include a base line mixture of RJ and SJ to be constant throughout the test, with the larger SJ used for the measurement summed into the baseline. The addition of the baseline represents the intended operating environment.

# 3 Operation

#### 3.1 General Information

The N4960A serial BERT should be used in accordance with the following:

- Read and follow operating instructions of all system equipment and do not exceed min/max specifications.

- Use ESD protection at all times, but especially when handling RF inputs/outputs.

- Before connecting any cable to the instrument, discharge the cable by shorting the center and outer connectors of the cable together to ground momentarily.

- Situate the instrument away from heat sources.

- Do not block airflow to the fans or exhaust vents and do not allow foreign material into enclosure.

- Do not modify the power plug or wall outlet to remove the third (ground) pin.

- Do not drop or shake the instrument, minimize vibration, and handle with care.

- Power must be turned off before connecting/disconnecting a remote head.

NOTE

There are no user-serviceable parts within. Return damaged instruments for factory-authorized repair. Refer to instrument warranty for more information.

#### 3.1.1 Performance Recommendations

The following recommendations ensure best performance:

- When using differential mode connection for outputs, ensure the cables are phase balanced. If the electrical length of one cable is a significant fraction of a unit interval longer than the other, the quality of the differential signal will be degraded.

- Keep cable lengths short and minimize number of cable bends.

It is not usually necessary to terminate unused outputs of a differential pair when a single ended signal is used. However, when the N4952A error detector is driven with a single ended signal, it is good practice to terminate the unused input to avoid errors from external noise.

#### 3.1.2 Connector Care

The N4960A serial BERT controller features high-quality SMA connectors for the front and rear panel input and output connections while the N4951A pattern generator and N4952A error detector use 2.92 mm. The N4951B pattern generators use type 2.4 mm connectors for data output and SMA for auxiliary input/output connectors. Connector damage will degrade signal fidelity.

Use high quality SMA-connectors on the SMA ports. Always leave dust jackets on unused ports. Tighten the connectors to 8 in-lbs (90 N-cm) to assure proper mating.

Refer to the N4960-90030 N495xA through N498xA Connector Care Reference Guide at <a href="https://www.Keysight.com/find/N4951A">www.Keysight.com/find/N4951A</a>.

Inspect the connectors for the following:

- Worn or damaged threads

- Scratches to mating surface

- Burrs and loose metal particles

- Dust or foreign material in the space surrounding the center pin

- Ensure that female contacts are straight and aligned

Clean the connectors as described in the following procedure. Cleaning connectors with alcohol shall only be done with the instruments power cord removed, and in a well-ventilated area. Allow all residual alcohol moisture to evaporate, and the fumes to dissipate prior to energizing the instrument.

- 1. Remove any dust or loose particles using a low-pressure air source.

- 2. Moisten a lint-free swab with isopropyl alcohol. Do not saturate the swab.

- 3. Minimize the wicking of the alcohol into the connector structure.

- 4. Clean the mating plane surfaces and threads.

- 5. Allow alcohol to evaporate, and then use a low-pressure air source to blow surfaces clean.

- 6. Make sure no particles or residue remains.

- 7. Inspect connector for damage.

# 3.2 Power on Settings

On power on, the instrument always returns to the factory preset settings, listed in **8 Appendix A Preset State**. Users who wish to quickly return to last used settings may save them in one of the 5 saved settings locations, and recall them on power on.

# 3.3 N4960A Serial BERT Controller Front Panel

The N4960A serial BERT controller front panel indicates the system status and contains the control panel for local operation of the instrument.

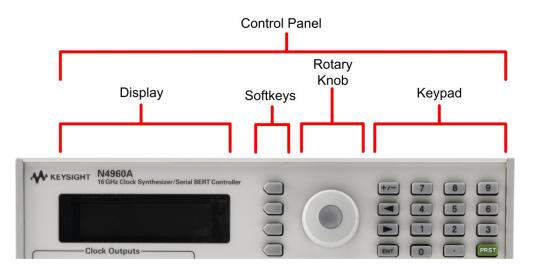

Figure 6 shows the front panel of the N4960A serial BERT controller.

Figure 6. N4960A serial BERT controller front panel

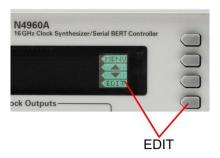

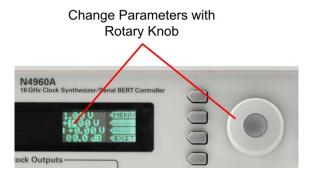

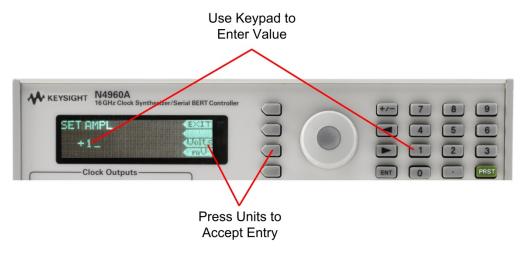

**Table 4** describes the N4960A serial BERT controller front panel functions.

Table 4. N4960A serial BERT controller front panel

| Item            | Description                                                                                                                                                                                 |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Display         | The display is part of the control panel and is used to view the menu structure.                                                                                                            |

| Softkey buttons | The four softkey buttons to the right of the display are part of the control panel and are used to switch between menu items, move the highlight up or down, and edit or select parameters. |

| Rotary knob     | The rotary knob is part of the control panel and is used to increase or decrease a numeric value and move the highlight to the next digit, character, or item in a list.                    |

| Keypad          | The keypad is part of the control panel and is used to enter numeric values for parameters. The PRST hardkey button is used to perform an instrument preset.                                |

| Item          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock outputs |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Jitter        | The jitter output is the main stressed clock output. The clock phase can be modulated in time with one or more calibrated jitter sources. The output amplitude, offset, and termination voltage are also user settable.  The jitter sources are:  Sinusoidal jitter 1 (SJ1) Sinusoidal jitter 2 (SJ2) (N4960A-CJ1 only) Sinusoidal periodic jitter (PJ) Externally supplied jitter Random jitter (RJ) is internally sourced (N4960A-CJ1 only) Sinusoidal jitter 1, Sinusoidal jitter 2, random jitter, and external jitter (high frequency band) can be enabled simultaneously. However, the sum of these paths must be kept below the specified maximum modulation level. In addition, the periodic jitter path or external low band (high deviation) jitter path cannot be enabled if any of the other jitter paths are enabled.  By disabling the stress sources, this output can be used to provide a clean (non-jittered) clock.  The jitter output also provides the clock source for the pattern generator. When used as a BERT, the synthesizer clock frequency is set to 1/2 of the |

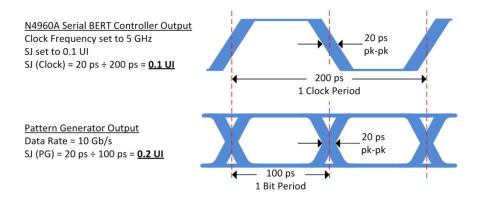

|               | BERT data rate. Any stress applied to the jitter clock output will appear on the pattern generator output (channel 0 only) at 2x the amplitude of the clock jitter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

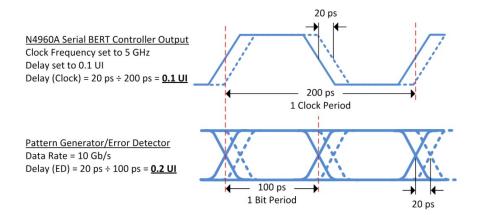

| Delay         | The delay differential output provides a non-stressed clock output with adjustable phase offset (in UI) as well as amplitude, offset, and termination voltage adjustment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|               | The delay clock is also used to clock the error detector. When operating as a BERT, both auto and manual detector alignment will alter the delay setting for the front panel output. Conversely, manually setting the delay output delay value may degrade the error detector operation by misaligning the detector sample point. The value of delay applied to the delay clock output will appear on the error detector or pattern generator output (channel 1 only) at 2x the value of the clock delay.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Divided       | The divided differential clock output produces a non-stressed signal that is related to the clock frequency by a divider factor. The divided clock output signal also has amplitude, offset, and termination voltage adjustment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|               | By setting the divide ratio to 1, this output can be used as a non-divided clean (non-jittered) clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Item           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ext Clock In   | Accepts an external clock to be substituted for the internal synthesizer across the entire supported frequency range. When used to source the clock for the pattern generator or error detector, this input is a half-rate clock.                                                                                                                                                                                                                                                                                             |

|                | Note: The instrument calibration requires knowledge of the clock frequency. To facilitate externally sourced clock input, it contains a frequency counter with sufficient resolution and accuracy to support this calibration. The counter and instrument systems require a finite time to respond to large frequency changes. Thus, in order to maintain calibration, the external clock must be either a stable CW (Continuous Wave) signal, or modulated over relatively low frequency (< 100 MHz) at low rates of change. |

| Delayed Clk In | Accepts an external signal which can be used to clock the error detector. This would commonly be sourced from an external clock recovery unit. When used with the error detector, this input is a half-rate clock (one half the error detector data rate).                                                                                                                                                                                                                                                                    |

|                | Note: The instrument calibration requires knowledge of the applied clock frequency. Unlike the external clock input, the instrument does not have an internal counter to determine the delay clock frequency, and so the frequency should be entered by the user. If no value is entered, the instrument defaults to the main clock frequency.                                                                                                                                                                                |

| Status LEDs    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Outputs On     | The Outputs On LED indicator is lit when any of the clock outputs are turned on.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Jitter On      | The Jitter On LED indicator is lit when any stress source is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SSC            | The SSC LED indicator is lit when the spread spectrum clock function is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Attention      | The Attention LED indicator is lit when an error has occurred. The indicator will not turn off until the error message has been cleared in the Error Log in the System menu.                                                                                                                                                                                                                                                                                                                                                  |

| Item   | Description                                                                                                                                                                                      |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Delay  | An error detector or pattern generator can be connected to the Delay connector (channel 1). The clock signal for the error detector or pattern generator is derived from the Delay clock output. |

| Jitter | A pattern generator can be connected to the Jitter connector (channel 0). The clock signal for the pattern generator is derived from the Jitter clock output.                                    |

# 3.4 N4960A Serial BERT Controller Rear Panel

Figure 7 shows the N4960A serial BERT controller rear panel.

Figure 7. N4960A serial BERT controller rear panel

Table 5 describes the N4960A serial BERT controller rear panel functions.

Table 5. N4960A serial BERT controller rear panel

| Item                           | Description                                                                                                                                                                               |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB Connector                  | The USB connector is a type B USB port that connects the N4960A serial BERT controller to an external PC for remote operation.                                                            |

| GPIB Connector                 | The GPIB connector is a general purpose interface bus (GPIB, IEEE 488.1) connection that can be used for remote operation.                                                                |

| Ext Jit In                     | Accepts an external jitter source for either the low or high frequency band modulation paths. Low band input must be sinusoidal wave shape, with frequency in the range of 1 Hz to 4 MHz. |

| RJ Out and RJ In<br>Connectors | The RJ loop through path is used for inserting modulation frequency contour filters in the random jitter path. The signal impedance is 50 $\Omega$ .                                      |

| Item                  | Description                                                                                                                                                                                                                                                                                                     |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10 MHz In Connector   | The 10 MHz In connector accepts a 10 MHz reference signal from an external source to allow the synthesizer to be phase locked to an external reference clock.                                                                                                                                                   |

| 10 MHz Out Connector  | The 10 MHz Out connector is a 10 MHz reference output used to lock the frequency reference of other equipment to the N4960 serial BERT controller.                                                                                                                                                              |

| Label                 | N4960A serial BERT controller serial number.                                                                                                                                                                                                                                                                    |

| Fuse Drawer           | Contains the primary power mains fuse. To replace, remove the fuse by depressing the snap in tab and withdrawing the fuse drawer. A blown primary fuse generally indicates a significant component failure. The instrument should be returned to Keysight Technologies for service in the event the fuse blows. |

| Power Switch          | N4960A serial BERT controller main power switch (1=0n; 0=0ff).                                                                                                                                                                                                                                                  |

| Power Input Connector | Connect to power mains using approved power cable.                                                                                                                                                                                                                                                              |

# 3.5 N4951A Front Panel

Figure 8. N4951A front panel Table 6. N4951A front panel

| Item        | Description                                                                                                                                                                  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ch ID LED   | The Channel ID LED indicator is lit when connected to the N4960A serial BERT controller.                                                                                     |

| Atten LED   | The Attention LED indicator is lit when an error has occurred. The indicator will not turn off until the error message has been cleared in the Error Log in the System menu. |

| On LED      |                                                                                                                                                                              |

| Output Off  | The On LED indicator is off when the data output is turned off.                                                                                                              |

| Output On   | The On LED indicator is lit when the data output is turned on.                                                                                                               |

| Data Output | The differential data outputs are 2.92 mm connectors.                                                                                                                        |

| Item       | Description                                                        |

|------------|--------------------------------------------------------------------|

| Connectors |                                                                    |

| Aux In     | This connector is reserved for future enhancements.                |

| Aux Out    | The Auxiliary Output 2.92 mm connector provides a pattern trigger. |

# 3.6 N4951A Rear Panel

Figure 9. N4951A rear panel

Table 7. N4951A rear panel

| Item                 | Description                                                                                                                                                |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Controller Connector | The D-subminiature connector receives clock signals, control signals, and power supplies from the controller via the 1 meter remote head/controller cable. |

| Label                | Shows the N4951A option number (-P17 or -P32) and serial number.                                                                                           |

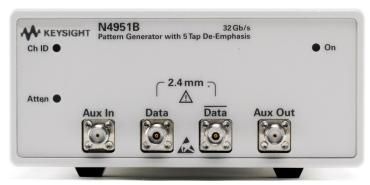

# 3.7 N4951B-D17/-D32 Front Panel

Figure 10. N4951B-D17/-D32 front panel Table 8. N4951B-D17/-D32 front panel

| Item                      | Description                                                                                                                                                                  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ch ID LED                 | The Channel ID LED indicator is lit when connected to the N4960A serial BERT controller.                                                                                     |

| Atten LED                 | The Attention LED indicator is lit when an error has occurred. The indicator will not turn off until the error message has been cleared in the Error Log in the System menu. |

| On LED                    |                                                                                                                                                                              |

| Output Off                | The On LED indicator is off when the data output is turned off.                                                                                                              |

| Output On                 | The On LED indicator is lit when the data output is turned on.                                                                                                               |

| Data Output<br>Connectors | The differential data outputs are 2.4 mm connectors.                                                                                                                         |

| Aux In                    | This connector is reserved for future enhancements.                                                                                                                          |

| Aux Out                   | The Auxiliary Output SMA connector provides a pattern trigger.                                                                                                               |

# 3.8 N4951B-D17/-D32 Rear Panel

Figure 11. N4951B-D17/-D32 rear panel

Table 9. N4951B-D17/-D32 rear panel

| Item                 | Description                                                                                                                                                |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Controller Connector | The D-subminiature connector receives clock signals, control signals, and power supplies from the controller via the 1 meter remote head/controller cable. |

| Label                | Shows the N4951B option number (-D17 or -D32) and serial number.                                                                                           |

# 3.9 N4951B-H17/-H32 Front Panel

Figure 12. N4951B-H17/-H32 front panel

Table 10. N4951B-H17/-H32 front panel

| Item                      | Description                                                                                                                                                                  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ch ID LED                 | The Channel ID LED indicator is lit when connected to the N4960A serial BERT controller.                                                                                     |

| Atten LED                 | The Attention LED indicator is lit when an error has occurred. The indicator will not turn off until the error message has been cleared in the Error Log in the System menu. |

| On LED                    |                                                                                                                                                                              |

| Output Off                | The On LED indicator is off when the data output is turned off.                                                                                                              |

| Output On                 | The On LED indicator is lit when the data output is turned on.                                                                                                               |

| Data Output<br>Connectors | The differential data outputs are 2.4 mm connectors.                                                                                                                         |

| Aux In                    | This connector is reserved for future enhancements.                                                                                                                          |

| Aux Out                   | The Auxiliary Output SMA connector provides a pattern trigger.                                                                                                               |

# 3.10 N4951B-H17/-H32 Rear Panel

Figure 13. N4951B-H17/-H32 rear panel Table 11. N4951B-H17/-H32 rear panel

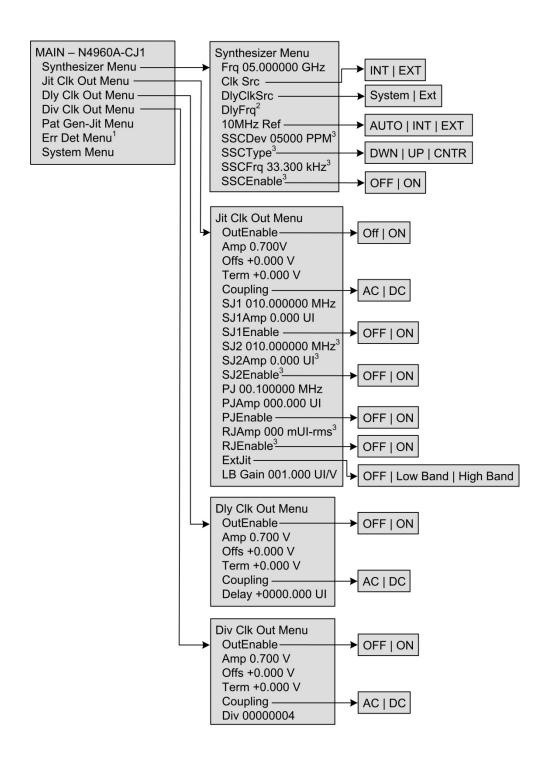

| Item                 | Description                                                                                                                                                |